MPC5604B/C Microcontroller Reference Manual, Rev. 8

Freescale Semiconductor 165

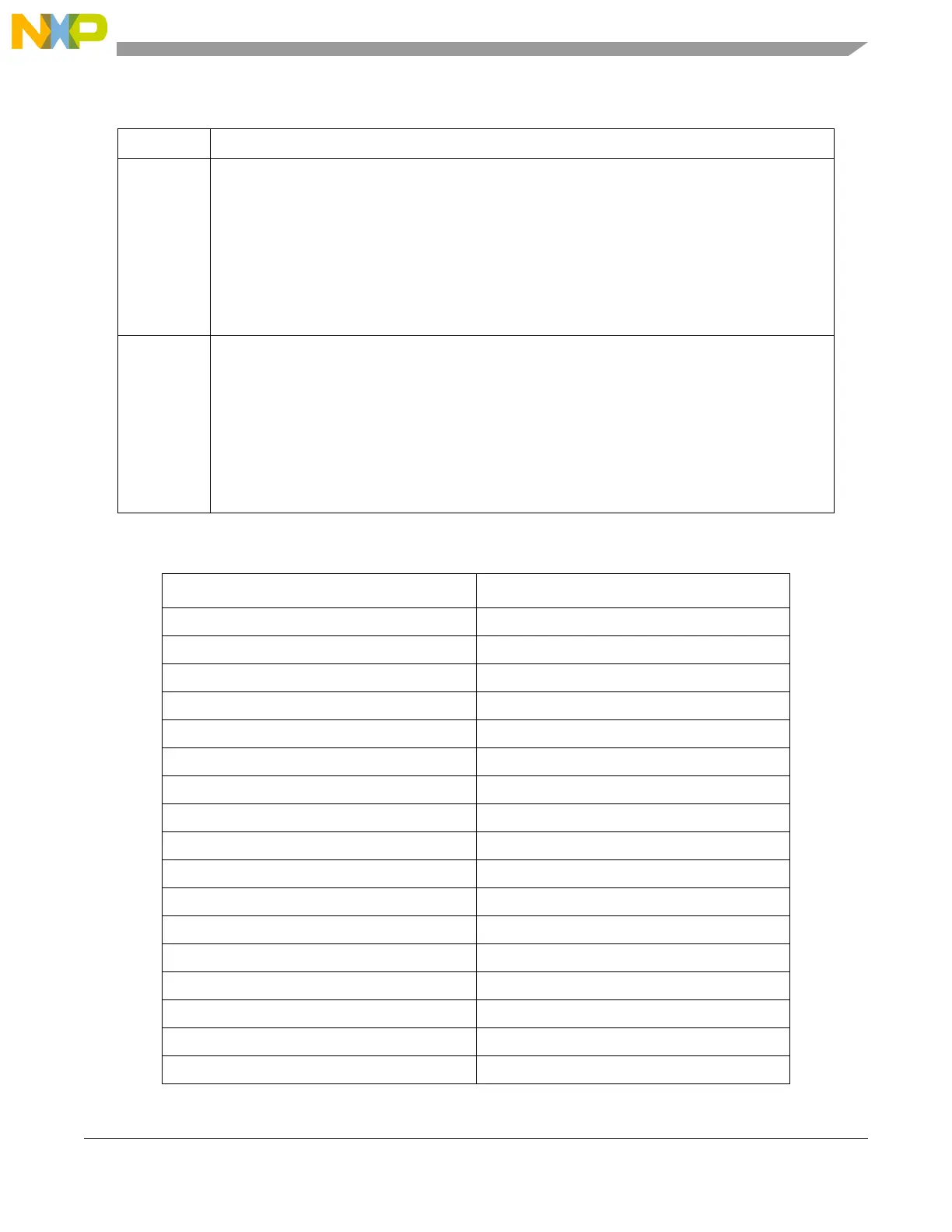

LP_CFG Peripheral configuration select for non-run modes — These bits associate a configuration as defined

in the ME_LP_PC0…7 registers to the peripheral.

000 Selects ME_LP_PC0 configuration

001 Selects ME_LP_PC1 configuration

010 Selects ME_LP_PC2 configuration

011 Selects ME_LP_PC3 configuration

100 Selects ME_LP_PC4 configuration

101 Selects ME_LP_PC5 configuration

110 Selects ME_LP_PC6 configuration

111 Selects ME_LP_PC7 configuration

RUN_CFG Peripheral configuration select for run modes — These bits associate a configuration as defined in

the ME_RUN_PC0…7 registers to the peripheral.

000 Selects ME_RUN_PC0 configuration

001 Selects ME_RUN_PC1 configuration

010 Selects ME_RUN_PC2 configuration

011 Selects ME_RUN_PC3 configuration

100 Selects ME_RUN_PC4 configuration

101 Selects ME_RUN_PC5 configuration

110 Selects ME_RUN_PC6 configuration

111 Selects ME_RUN_PC7 configuration

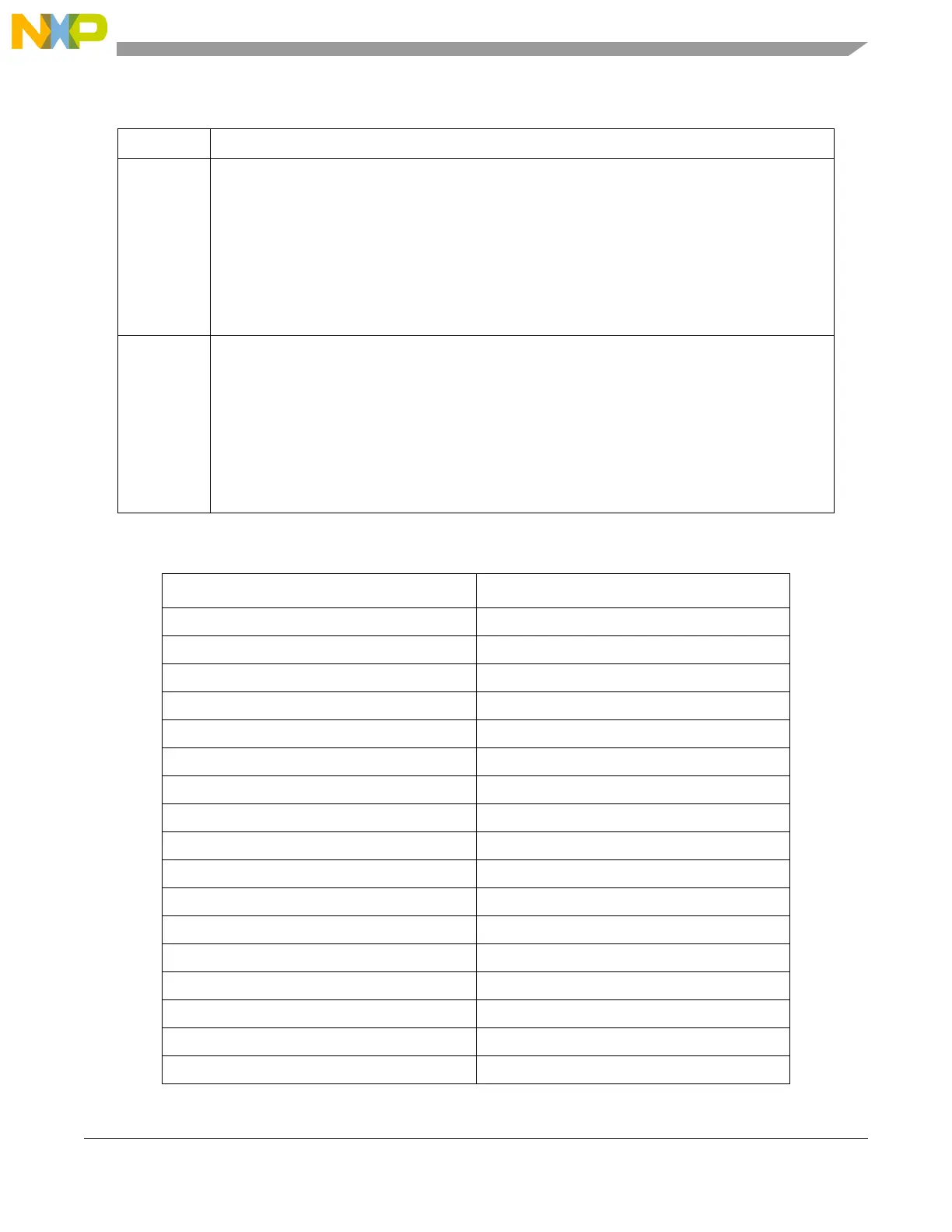

Table 8-16. Peripheral control registers by peripheral

Peripheral ME_PCTLn

ADC_0 32

CAN sampler 60

CMU 104

CTU 57

DMA_MUX 23

DSPI_0 4

DSPI_1 5

DSPI_2 6

DSPI_3 7

eMIOS_0 72

eMIOS_1 73

FlexCAN_0 16

FlexCAN_1 17

FlexCAN_2 18

FlexCAN_3 10

FlexCAN_4 20

FlexCAN_5 21

Table 8-15. Peripheral Control Registers (ME_PCTL0…143) Field Descriptions (continued)

Field Description

Loading...

Loading...