MPC5604B/C Microcontroller Reference Manual, Rev. 8

474 Freescale Semiconductor

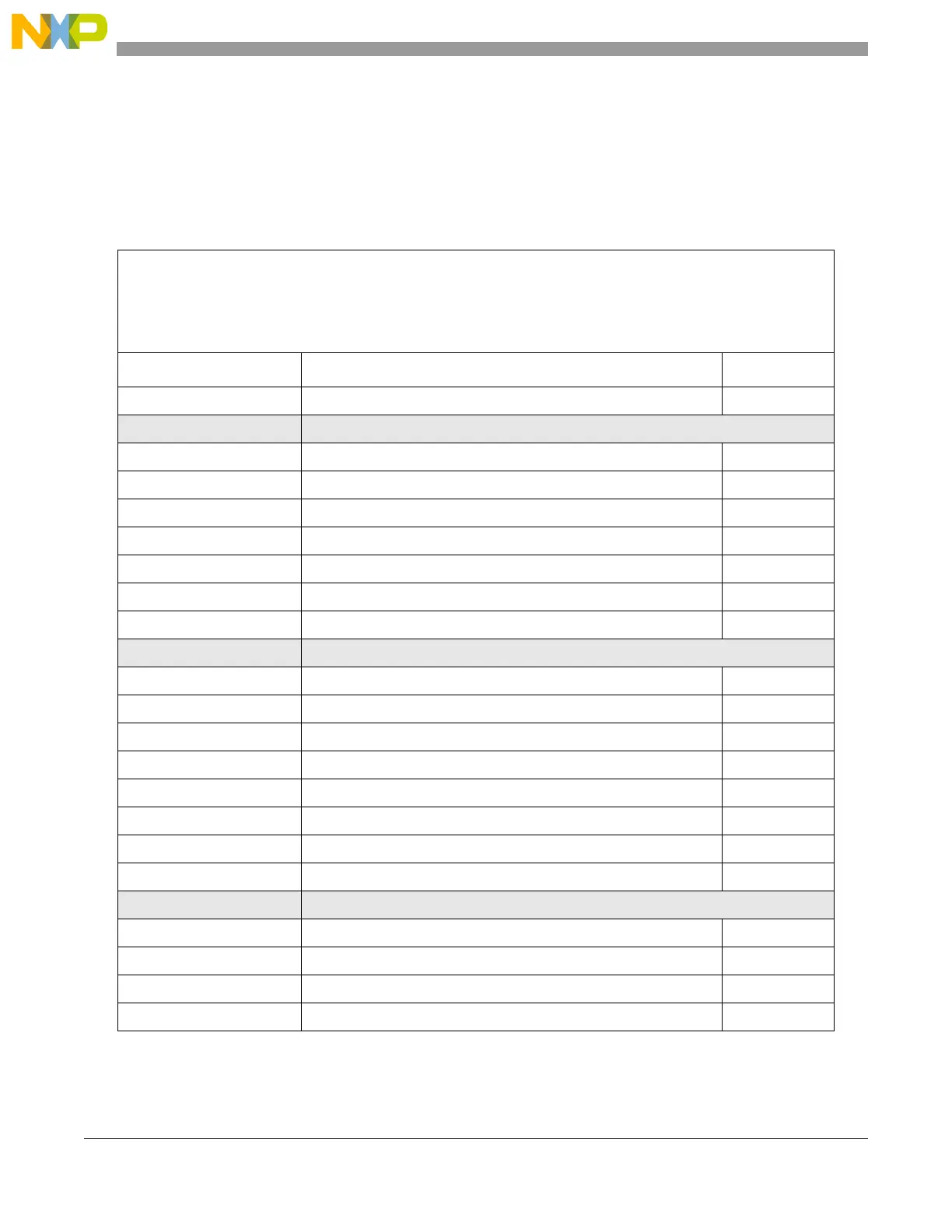

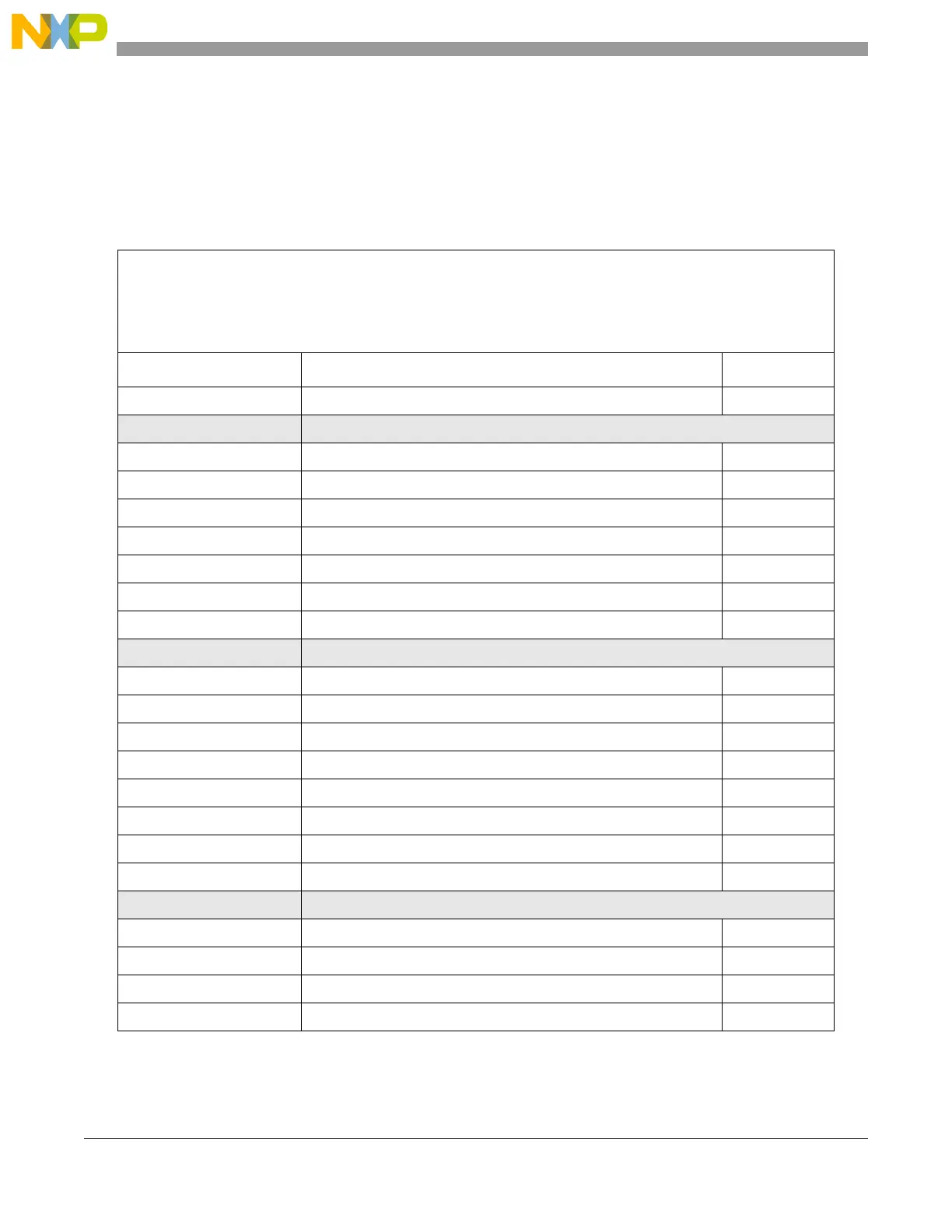

23.5 Memory map and register description

23.5.1 Memory map

Table 23-2 shows the DSPI memory map.

Table 23-2. DSPI memory map

Base addresses:

0xFFF9_0000 (DSPI_0)

0xFFF9_4000 (DSPI_1)

0xFFF9_8000 (DSPI_2)

Address offset Register Location

0x00 DSPI Module Configuration Register (DSPIx_MCR) on page 475

0x04 Reserved

0x08 DSPI Transfer Count Register (DSPIx_TCR) on page 478

0x0C DSPI Clock and Transfer Attributes Register 0 (DSPIx_CTAR0) on page 478

0x10 DSPI Clock and Transfer Attributes Register 1 (DSPIx_CTAR1) on page 478

0x14 DSPI Clock and Transfer Attributes Register 2 (DSPIx_CTAR2) on page 478

0x18 DSPI Clock and Transfer Attributes Register 3 (DSPIx_CTAR3) on page 478

0x1C DSPI Clock and Transfer Attributes Register 4 (DSPIx_CTAR4) on page 478

0x20 DSPI Clock and Transfer Attributes Register 5 (DSPIx_CTAR5) on page 478

0x24–0x28 Reserved

0x2C DSPI Status Register (DSPIx_SR) on page 486

0x30 DSPI Interrupt Request Enable Register (DSPIx_RSER) on page 488

0x34 DSPI Push TX FIFO Register (DSPIx_PUSHR) on page 490

0x38 DSPI Pop RX FIFO Register (DSPIx_POPR) on page 492

0x3C DSPI Transmit FIFO Register 0 (DSPIx_TXFR0) on page 493

0x40 DSPI Transmit FIFO Register 1 (DSPIx_TXFR1) on page 493

0x44 DSPI Transmit FIFO Register 2 (DSPIx_TXFR2) on page 493

0x48 DSPI Transmit FIFO Register 3 (DSPIx_TXFR3) on page 493

0x4C–0x78 Reserved

0x7C DSPI Receive FIFO Register 0 (DSPIx_RXFR0) on page 493

0x80 DSPI Receive FIFO Register 1 (DSPIx_RXFR1) on page 493

0x84 DSPI Receive FIFO Register 2 (DSPIx_RXFR2) on page 493

0x88 DSPI Receive FIFO Register 3 (DSPIx_RXFR3) on page 493

Loading...

Loading...