MPC5604B/C Microcontroller Reference Manual, Rev. 8

250 Freescale Semiconductor

13.5.4 RTC Counter Register (RTCCNT)

The RTCCNT register contains the current value of the RTC counter.

13.6 RTC functional description

The RTC consists of a 32-bit free running counter enabled with the RTCC[CNTEN] bit (CNTEN when

negated asynchronously resets the counter and synchronously enables the counter when enabled). The

value of the counter may be read via the RTCCNT register. Note that due to the clock synchronization, the

RTCCNT value may actually represent a previous counter value. The difference between the counter and

the read value depends on ratio of counter clock and system clock. Maximum possible difference between

the two is 6 count values.

The clock source to the counter is selected with the RTCC[CLKSEL] field, which gives the options for

clocking the RTC/API. The output of the clock mux can be optionally divided by combination of 512 and

32 to give a 1 ms RTC/API count period for different clock sources. Note that the RTCC[CNTEN] bit must

be disabled when the RTC/API clock source is switched.

When the counter value for counter bits 10:21 match the 12-bit value in the RTCC[RTCVAL] field, then

the RTCS[RTCF] interrupt flag bit is set (after proper clock synchronization). If the RTCC[RTCIE]

interrupt enable bit is set, then the RTC interrupt request is generated. The RTC supports interrupt requests

in the range of 1 s to 4096 s (> 1 hr) with a 1 s resolution. If there is a match while in low power mode then

the RTC will first generate a wakeup request to force a wakeup to run mode, then the RTCF flag will be set.

A rollover wakeup and/or interrupt can be generated when the RTC transitions from a count of

0xFFFF_FFFF to 0x0000_0000. The rollover flag is enabled by setting the RTCC[ROVREN] bit. An RTC

counter rollover with this bit will cause a wakeup from low power mode. An interrupt request is generated

for an RTC counter rollover when both the RTCC[ROVREN] and RTCC[RTCIE] bits are set.

All the flags and counter values are synchronized with the system clock. It is assumed that the system clock

frequency is always more than or equal to the rtc_clk used to run the counter.

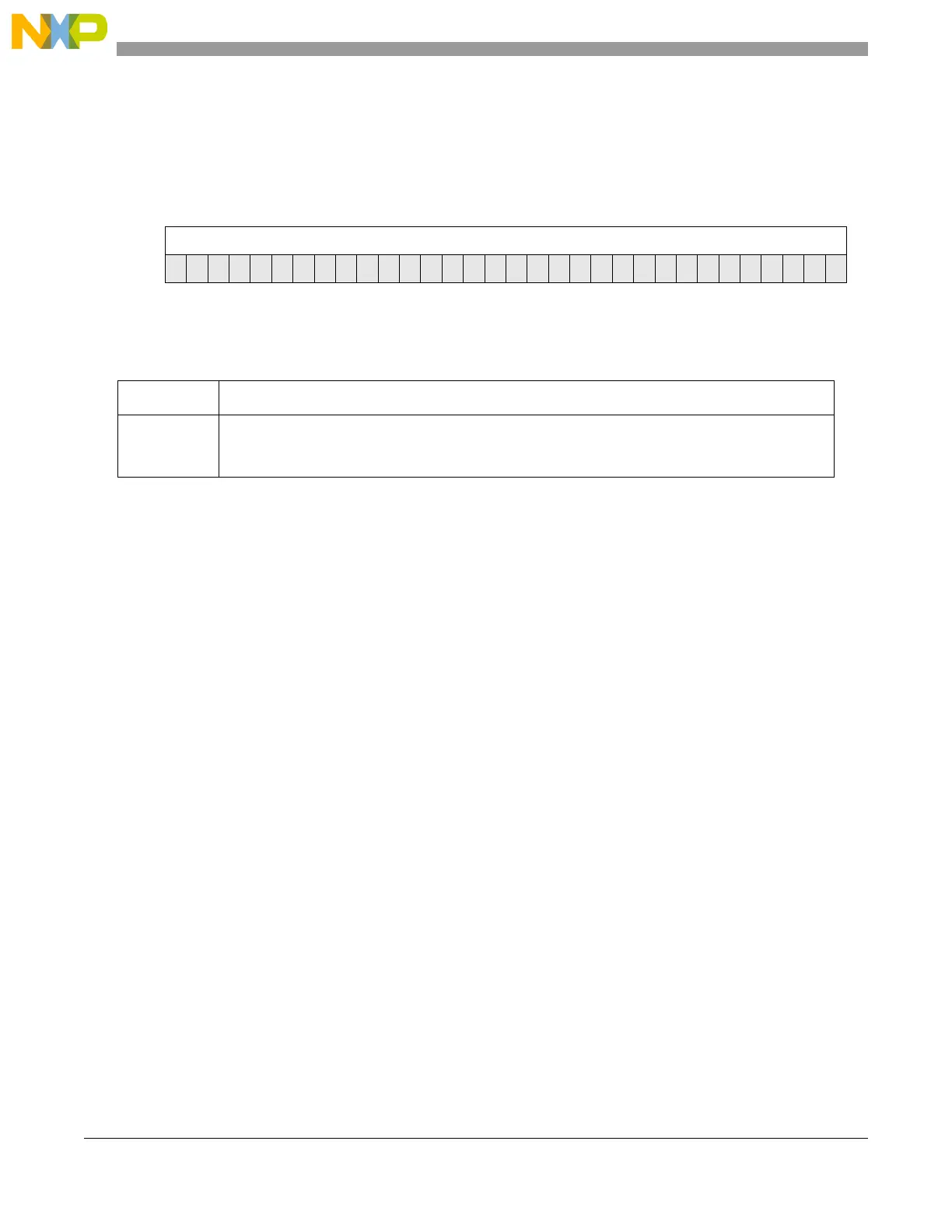

Offset: 0xC Access: Read

012345678910111213141516171819202122232425262728293031

R RTCCNT

W

Reset00000000000000000000000000000000

Figure 13-6. RTC Counter Register (RTCCNT)

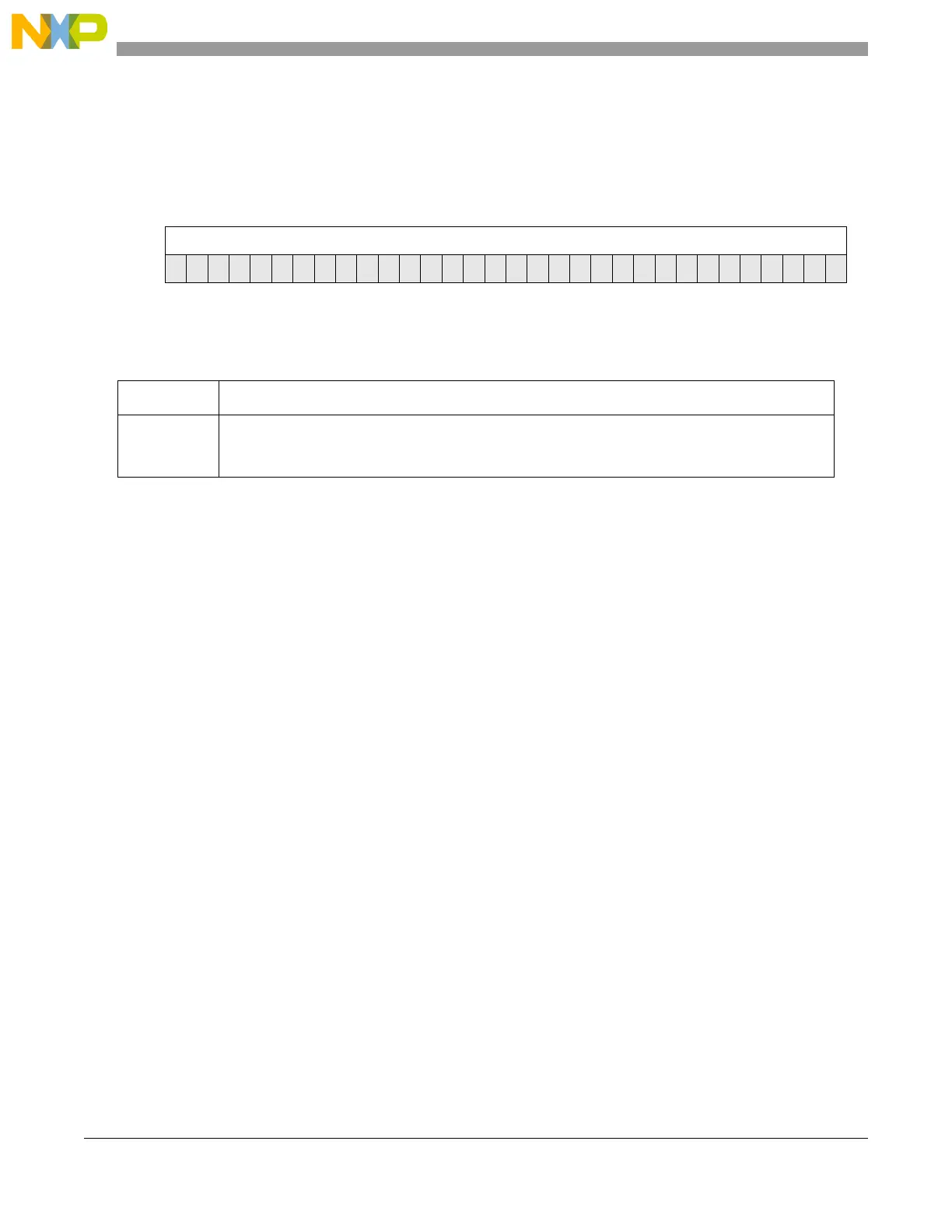

Table 13-5. RTCCNTfield descriptions

Field Description

RTCCNT RTC Counter Value

Due to the clock synchronization, the RTCCNT value may actually represent a previous counter

value.

Loading...

Loading...