MPC5604B/C Microcontroller Reference Manual, Rev. 8

Freescale Semiconductor 847

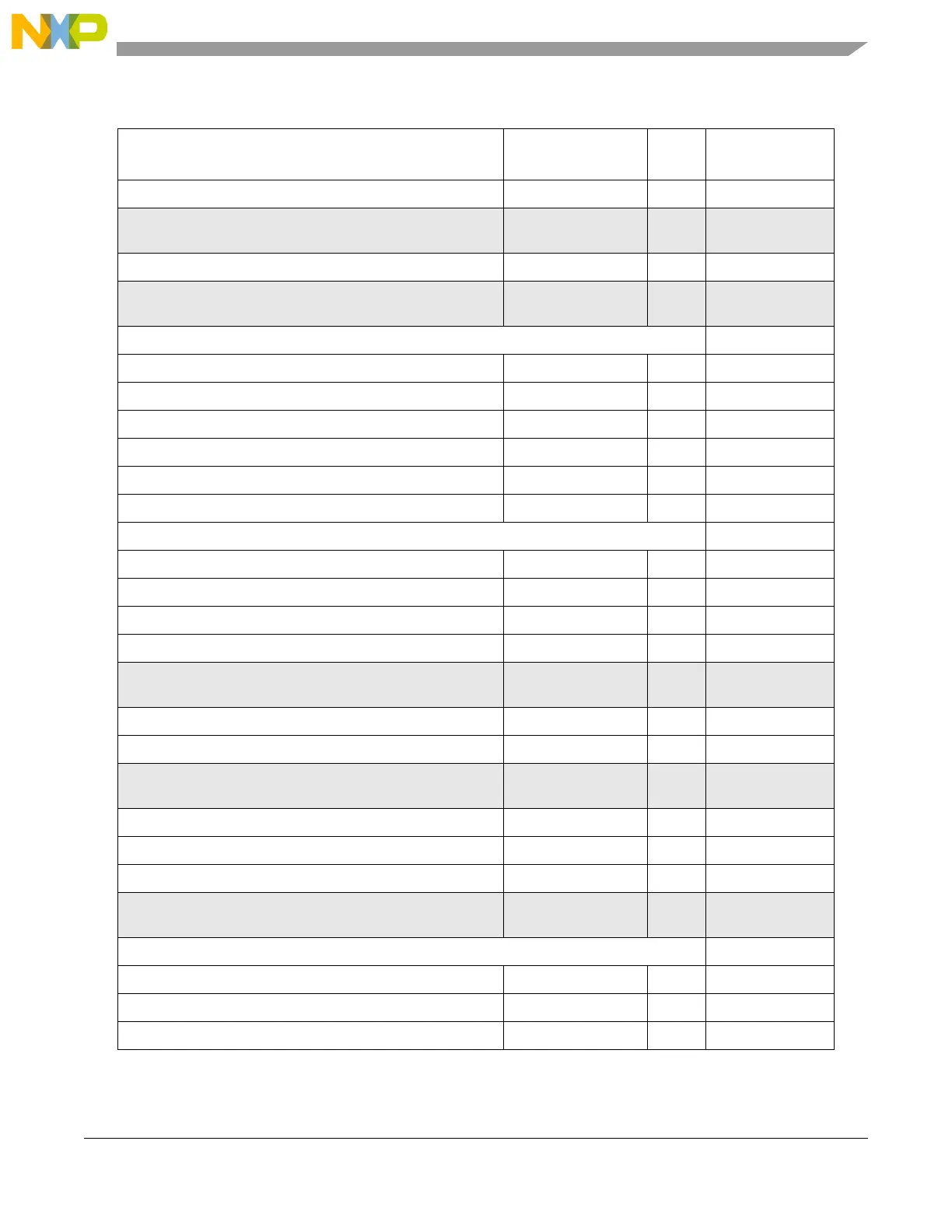

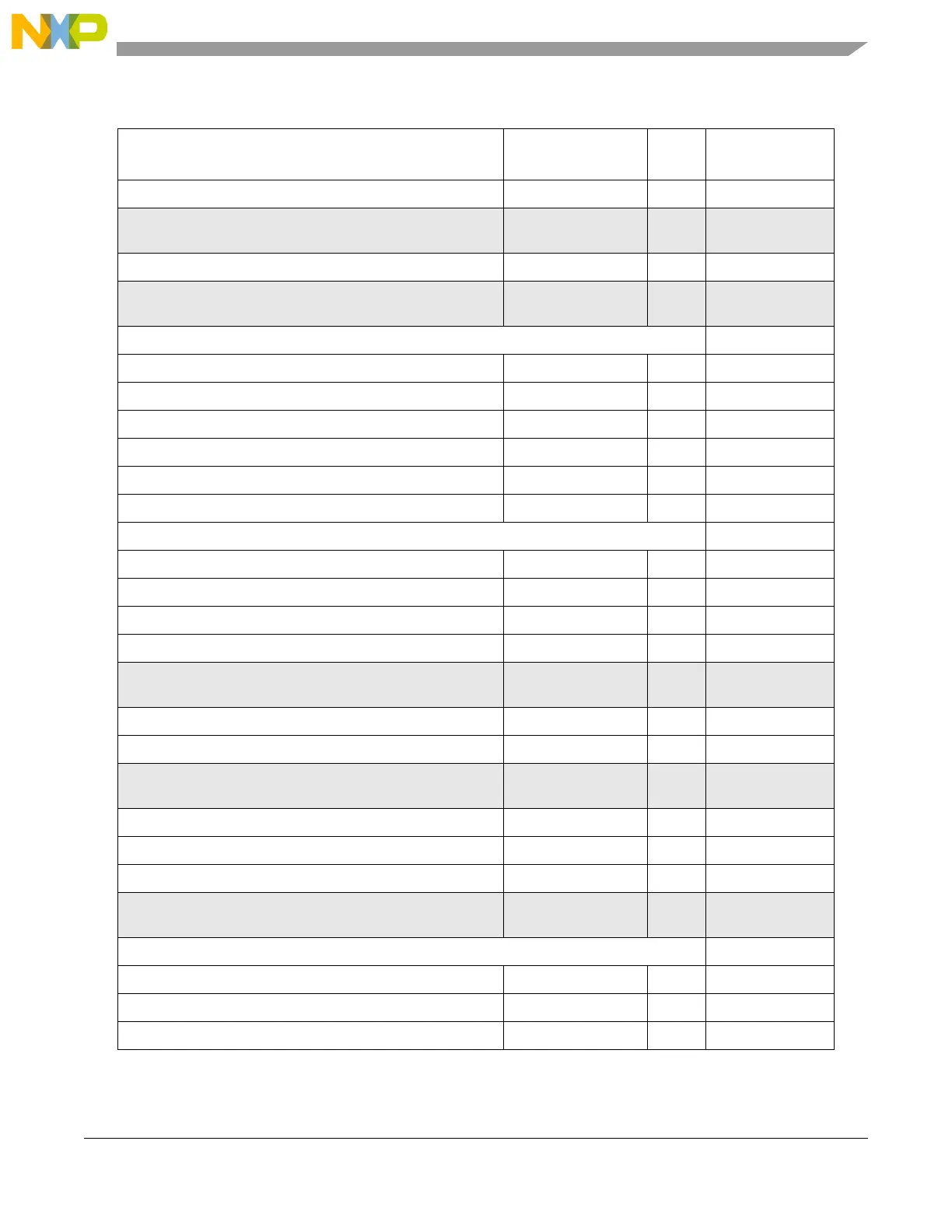

Interrupt Status Register CMU_ISR 32-bit Base + 0x0010

Reserved — — (Base + 0x0014) –

(Base + 0x0017)

Measurement Duration Register CMU_MDR 32-bit Base + 0x0018

Reserved — — (Base + 0x001C) –

(Base + 0x036F)

Clock Generation Module (MC_CGM) 0xC3FE_0370

Output Clock Enable Register CGM_OC_EN 32-bit Base + 0x0000

Output Clock Division Select Register CGM_OCDS_SC 32-bit Base + 0x0004

System Clock Select Status Register CGM_SC_SS 32-bit Base + 0x0008

System Clock Divider Configuration 0 Registers CGM_SC_DC0 8-bit Base + 0x000C

System Clock Divider Configuration 1 Registers CGM_SC_DC1 8-bit Base + 0x000D

System Clock Divider Configuration 2 Registers CGM_SC_DC2 8-bit Base + 0x000E

Reset Generation Module (MC_RGM) 0xC3FE_4000

Functional Event Status RGM_FES 16-bit Base + 0x0000

Destructive Event Status RGM_DES 16-bit Base + 0x0002

Functional Event Reset Disable RGM_FERD 16-bit Base + 0x0004

Destructive Event Reset Disable RGM_DERD 16-bit Base + 0x0006

Reserved — — (Base + 0x0008) –

(Base + 0x000F)

Functional Event Alternate Request RGM_FEAR 16-bit Base + 0x0010

Destructive Event Alternate Request RGM_DEAR 16-bit Base + 0x0012

Reserved — — (Base + 0x0014) –

(Base + 0x0017)

Functional Event Short Sequence RGM_FESS 16-bit Base + 0x0018

STANDBY reset sequence RGM_STDBY 16-bit Base + 0x001A

Functional Bidirectional Reset Enable RGM_FBRE 16-bit Base + 0x001C

Reserved — — (Base + 0x001E) –

(Base + 0x3FFF)

Power Control Unit (MC_PCU) 0xC3FE_8000

Power domain #0 configuration register PCONF0 32-bit Base + 0x0000

Power domain #1 configuration register PCONF1 32-bit Base + 0x0004

Power domain #2 configuration register PCONF2 32-bit Base + 0x0008

Table A-2. Detailed register map (continued)

Register description Register name

Used

size

Address

Loading...

Loading...