MPC5604B/C Microcontroller Reference Manual, Rev. 8

744 Freescale Semiconductor

29.5.2 Register description

29.5.2.1 Module Registers (MR0-6143)

This is the lower 6 KB module memory space which holds all the functional registers of the module that

is protected by the Register Protection module.

29.5.2.2 Module Register and Set Soft Lock Bit (LMR0-6143)

This is memory area #3 that provides mirrored access to the MR0-6143 registers with the side effect of

setting soft lock bits in case of a write access to a MR that is defined as protectable by the locking

mechanism. Each MR is protectable by one associated bit in a SLBRn.SLBm, according to the mapping

described in Table 29-2.

29.5.2.3 Soft Lock Bit Register (SLBR0-1535)

These registers hold the soft lock bits for the protected registers in memory area #1.

Figure 29-3 gives some examples how SLBRn.SLB and MRn go together.

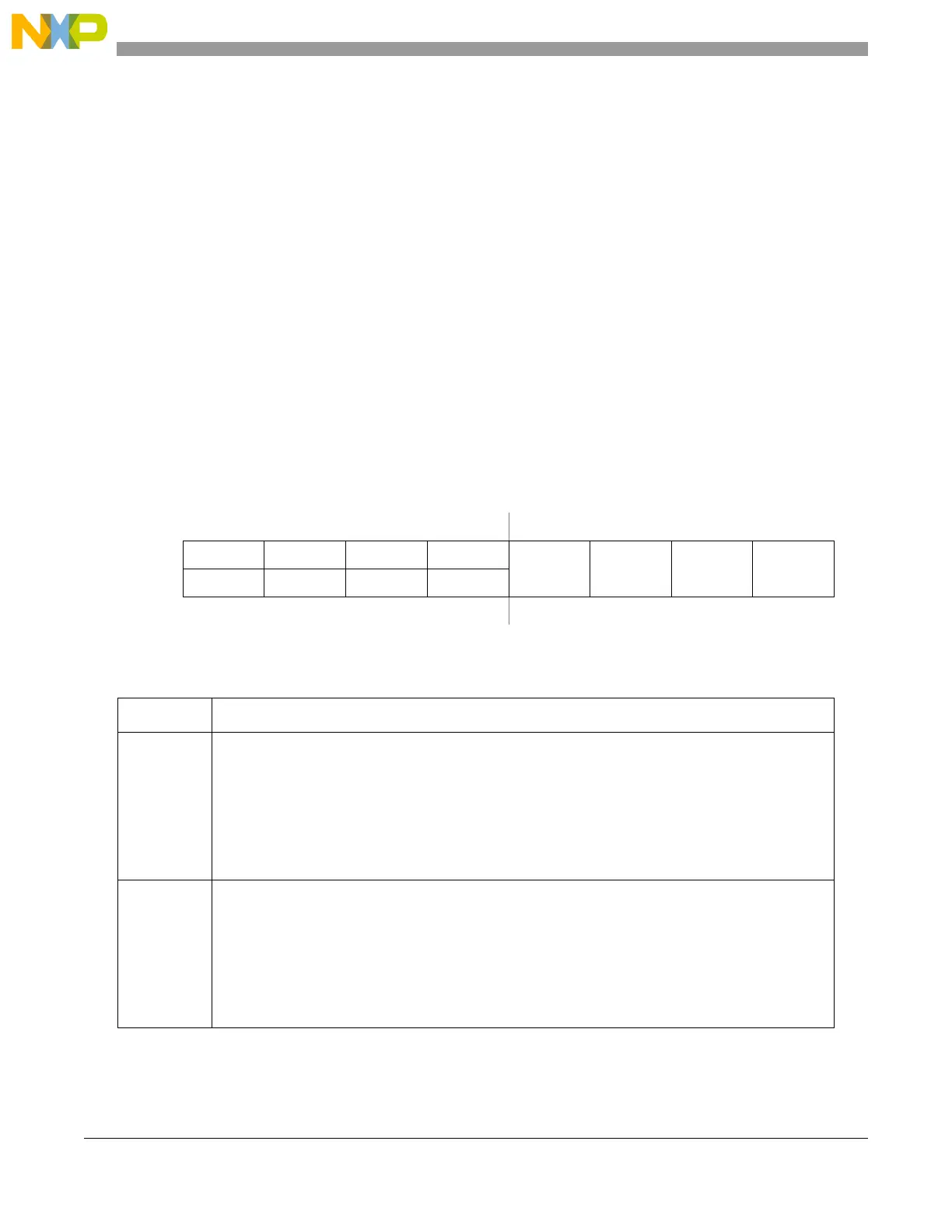

Address 0x3800-0x3DFF Access: Read always

Supervisor write

01234567

R0000

SLB0 SLB1 SLB2 SLB3

WWE0 WE1 WE2 WE3

Reset00000000

Figure 29-3. Soft Lock Bit Register (SLBRn)

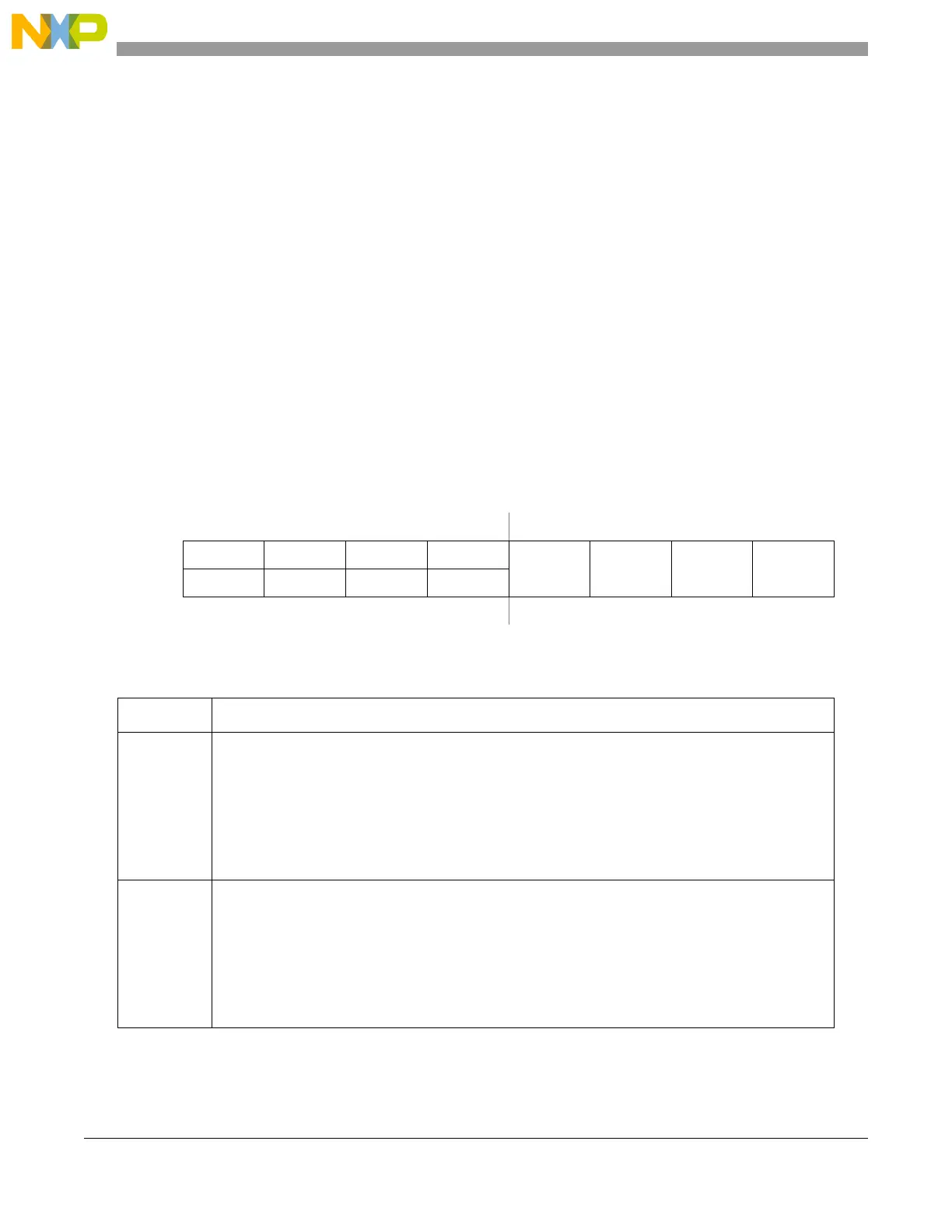

Table 29-2. SLBRn field descriptions

Field Description

WE0

WE1

WE2

WE3

Write Enable Bits for soft lock bits (SLB):

WE0 enables writing to SLB0

WE1 enables writing to SLB1

WE2 enables writing to SLB2

WE3 enables writing to SLB3

1 Value is written to SLB

0 SLB is not modified

SLB0

SLB1

SLB2

SLB3

Soft lock bits for one MRn register:

SLB0 can block accesses to MR[n *4 + 0]

SLB1 can block accesses to MR[n *4 + 1]

SLB2 can block accesses to MR[n *4 + 2]

SLB3 can block accesses to MR[n *4 + 3]

1 Associated MRn byte is locked against write accesses

0 Associated MRn byte is unprotected and writeable

Loading...

Loading...