MPC5604B/C Microcontroller Reference Manual, Rev. 8

486 Freescale Semiconductor

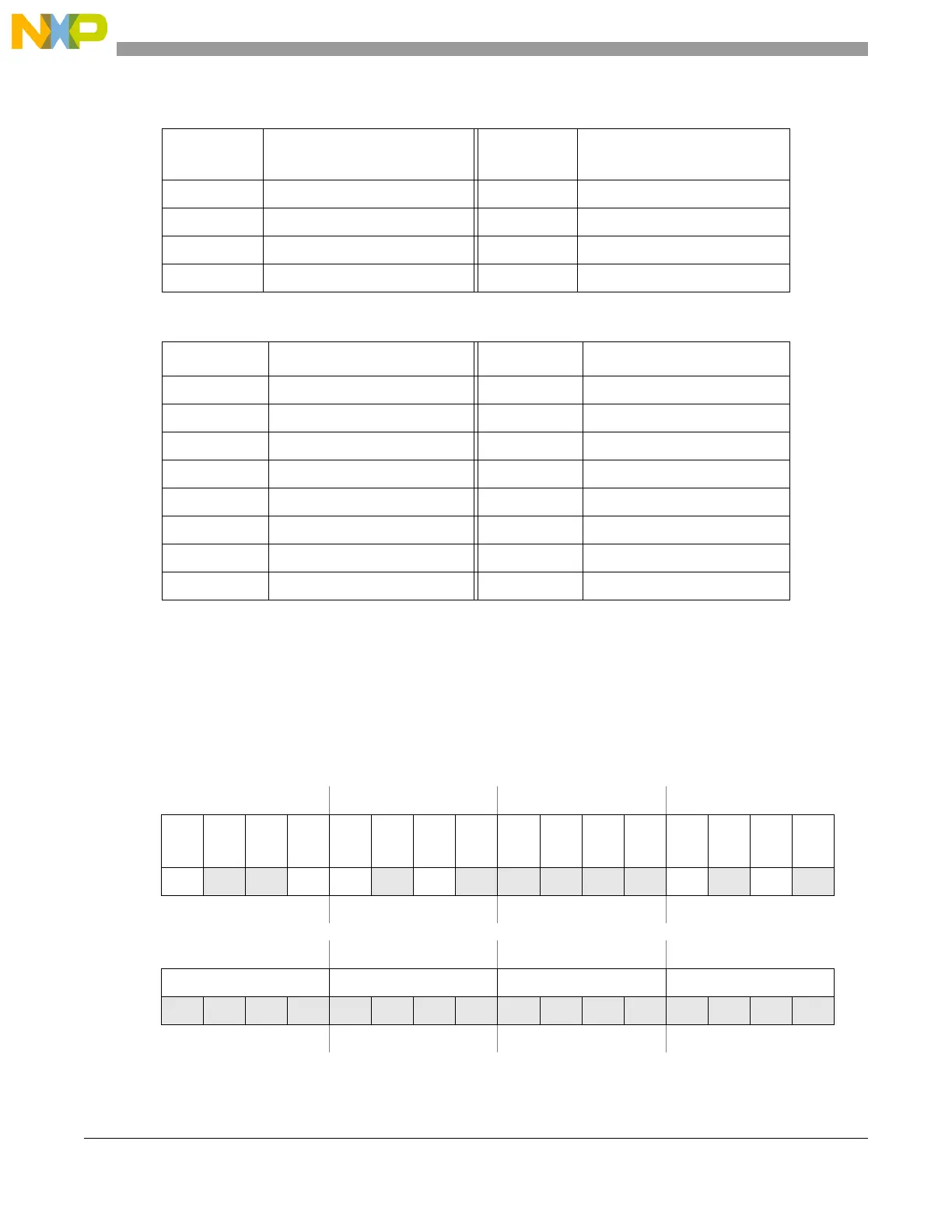

23.5.5 DSPI Status Register (DSPIx_SR)

The DSPIx_SR contains status and flag bits. The bits are set by the hardware and reflect the status of the

DSPI and indicate the occurrence of events that can generate interrupt requests. Software can clear flag

bits in the DSPIx_SR by writing a ‘1’ to clear it (w1c). Writing a ‘0’ to a flag bit has no effect. This register

may not be writable in Module Disable mode due to the use of power saving mechanisms.

0100 32 1100 8192

0101 64 1101 16384

0110 128 1110 32768

0111 256 1111 65536

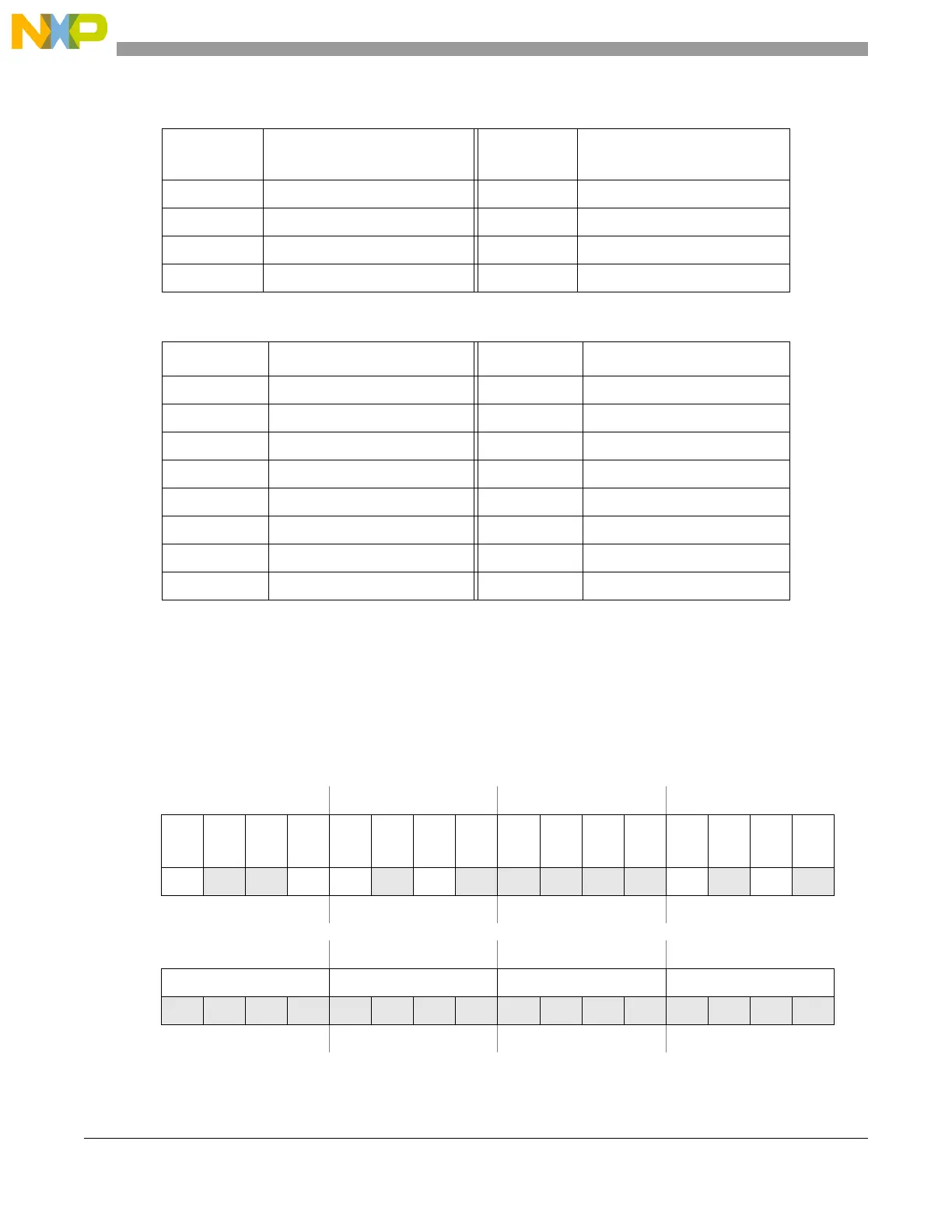

Table 23-17. DSPI baud rate scaler

BR Baud rate scaler value BR Baud rate scaler value

0000 2 1000 256

0001 4 1001 512

0010 6 1010 1024

0011 8 1011 2048

0100 16 1100 4096

0101 32 1101 8192

0110 64 1110 16384

0111 128 1111 32768

Offset: 0x2C Access: R/W

0123456789101112131415

R

TCF

TXRXS

0

EOQF

TFUF0TFFF00000

RFOF

0

RFDF

0

W

w1c w1c w1c w1c w1c w1c

Reset0000001000000000

16 17 18 19 20 21 22 23 24 25 26 27 28 29 30 31

R TXCTR TXNXTPTR RXCTR POPNXTPTR

W

Reset0000000000000000

Figure 23-6. DSPI Status Register (DSPIx_SR)

Table 23-16. DSPI delay after transfer scaler (continued) (continued)

DT

Delay after transfer scaler

value

DT

Delay after transfer scaler

value

Loading...

Loading...