MPC5604B/C Microcontroller Reference Manual, Rev. 8

850 Freescale Semiconductor

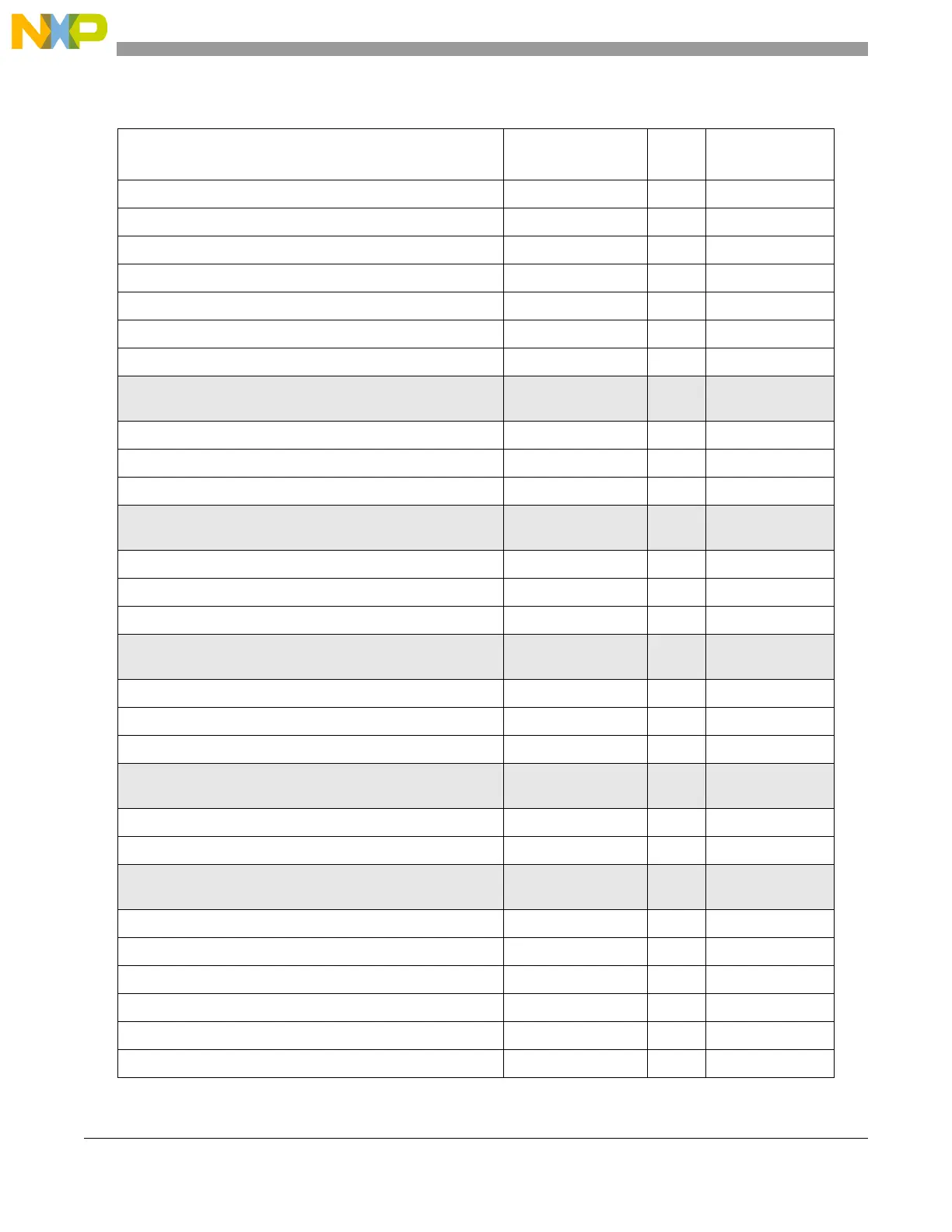

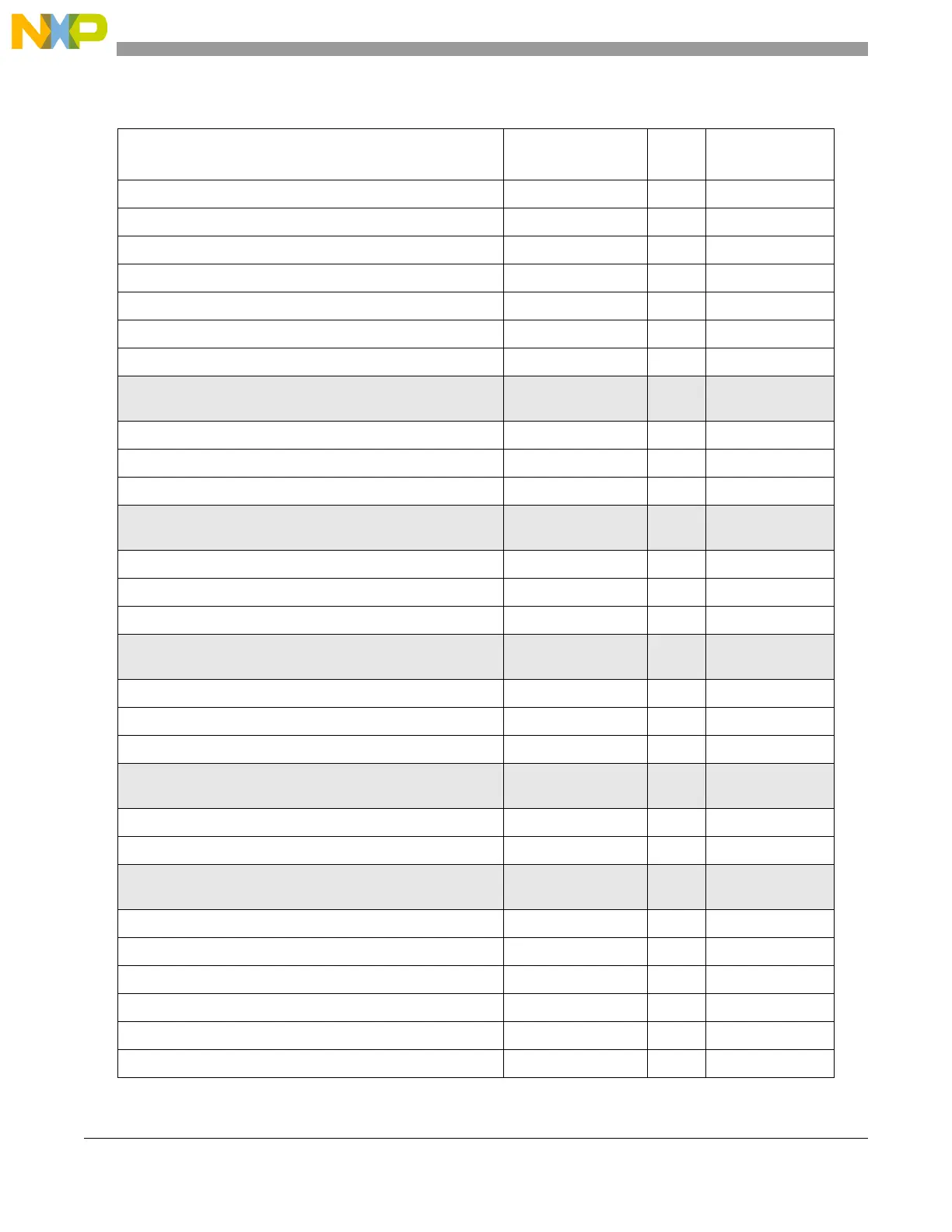

Threshold Register 1 THRHLR1 32-bit Base + 0x0064

Threshold Register 2 THRHLR2 32-bit Base + 0x0068

Threshold Register 3 THRHLR3 32-bit Base + 0x006C

Presampling Control Register PSCR 32-bit Base + 0x0080

Presampling Register 0 PSR0 32-bit Base + 0x0084

Presampling Register 1 PSR1 32-bit Base + 0x0088

Presampling Register 2 PSR2 32-bit Base + 0x008C

Reserved — — Base + 0x0090 –

0x0093

Conversion Timing Register 0 CTR0 32-bit Base + 0x0094

Conversion Timing Register 1 CTR1 32-bit Base + 0x0098

Conversion Timing Register 2 CTR2 32-bit Base + 0x009C

Reserved — — Base + 0x00A0 –

0x00A3

Normal Conversion Mask Register 0 NCMR0 32-bit Base + 0x00A4

Normal Conversion Mask Register 1 NCMR1 32-bit Base + 0x00A8

Normal Conversion Mask Register 2 NCMR2 32-bit Base + 0x00AC

Reserved — — Base + 0x00B0 –

0x00B3

Injected Conversion Mask Register 0 JCMR0 32-bit Base + 0x00B4

Injected Conversion Mask Register 1 JCMR1 32-bit Base + 0x00B8

Injected Conversion Mask Register 2 JCMR2 32-bit Base + 0x00BC

Reserved — — Base + 0x00C0 –

0x00C3

Decode Signals Delay Register DSDR 32-bit Base + 0x00C4

Power-down Exit Delay Register PDEDR 32-bit Base + 0x00C8

Reserved — — Base + 0x00CC –

0x00FF

Channel 0 Data Register CDR0 32-bit Base + 0x0100

Channel 1 Data Register CDR1 32-bit Base + 0x0104

Channel 2 Data Register CDR2 32-bit Base + 0x0108

Channel 3 Data Register CDR3 32-bit Base + 0x010C

Channel 4 Data Register CDR4 32-bit Base + 0x0110

Channel 5 Data Register CDR5 32-bit Base + 0x0114

Table A-2. Detailed register map (continued)

Register description Register name

Used

size

Address

Loading...

Loading...