MPC5604B/C Microcontroller Reference Manual, Rev. 8

Freescale Semiconductor 757

30.5.2 Register description

30.5.2.1 SWT Control Register (SWT_CR)

The SWT_CR contains fields for configuring and controlling the SWT. The reset value of this register is

device specific. Some devices can be configured to automatically clear the SWT_CR.WEN bit during the

boot process. This register is read only if either the SWT_CR.HLK or SWT_CR.SLK bits are set.

Default value for SWT_CR_RST is 0x4000_011B, corresponding to MAP1 = 1 (only data bus access

allowed), RIA = 1 (reset on invalid SWT access), SLK = 1 (soft lock), CSL = 1 (IRC clock source for

counter), FRZ = 1 (freeze on debug), WEN = 1 (watchdog enable). This last bit is cleared when exiting

ME RESET mode in case flash user option bit 31 (WATCHDOG_EN) is ‘0’.

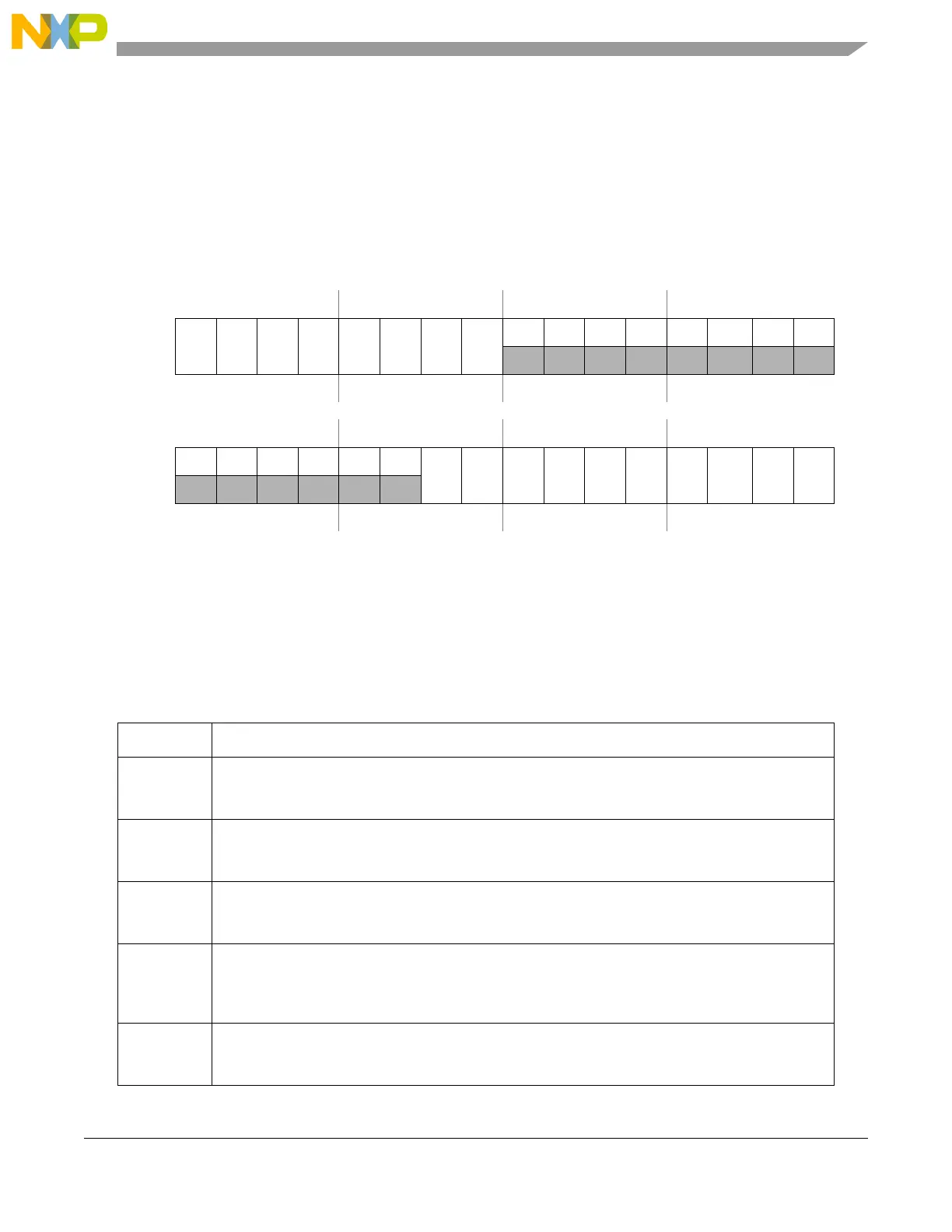

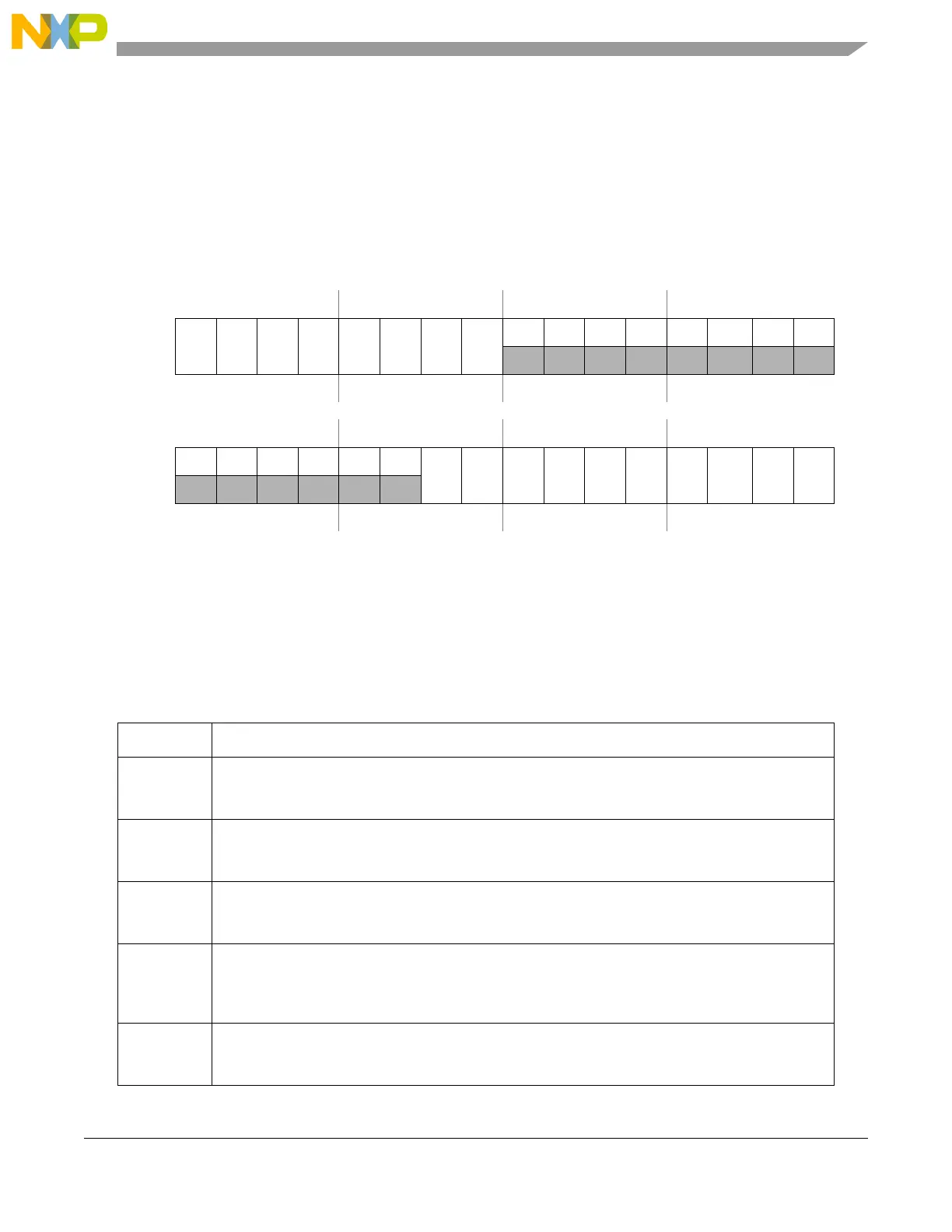

Offset 0x0000 Access: Read/Write

0 1 2 3 4 5 6 7 8 9 10 11 12 13 14 15

R

MAP

0

MAP

1

MAP

2

MAP

3

MAP

4

MAP

5

MAP

6

MAP

7

00000 0 00

W

Reset

1

0100000000000 0 00

16 17 18 19 20 21 22 23 24 25 26 27 28 29 30 31

R

0 00000

KEY RIA WND ITR HLK SLK CSL STP FRZ WEN

W

Reset

1

0000000100011 0 11

1

The reset value for the SWT_CR is device specific.

Figure 30-1. SWT Control Register (SWT_CR)

Table 30-2. SWT_CR field descriptions

Field Description

MAPn Master Access Protection for Master n. The platform bus master assignments are device specific.

0 = Access for the master is not enabled

1 = Access for the master is enabled

KEY Keyed Service Mode.

0 = Fixed Service Sequence, the fixed sequence 0xA602, 0xB480 is used to service the watchdog

1 = Keyed Service Mode, two pseudorandom key value are used to service the watchdog

RIA Reset on Invalid Access.

0 = Invalid access to the SWT generates a bus error

1 = Invalid access to the SWT causes a system reset if WEN=1

WND Window Mode.

0 = Regular mode, service sequence can be done at any time

1 = Windowed mode, the service sequence is only valid when the down counter is less than the value

in the SWT_WN register.

ITR Interrupt Then Reset.

0 = Generate a reset on a time-out

1 = Generate an interrupt on an initial time-out, reset on a second consecutive time-out

Loading...

Loading...