MPC5604B/C Microcontroller Reference Manual, Rev. 8

Freescale Semiconductor 351

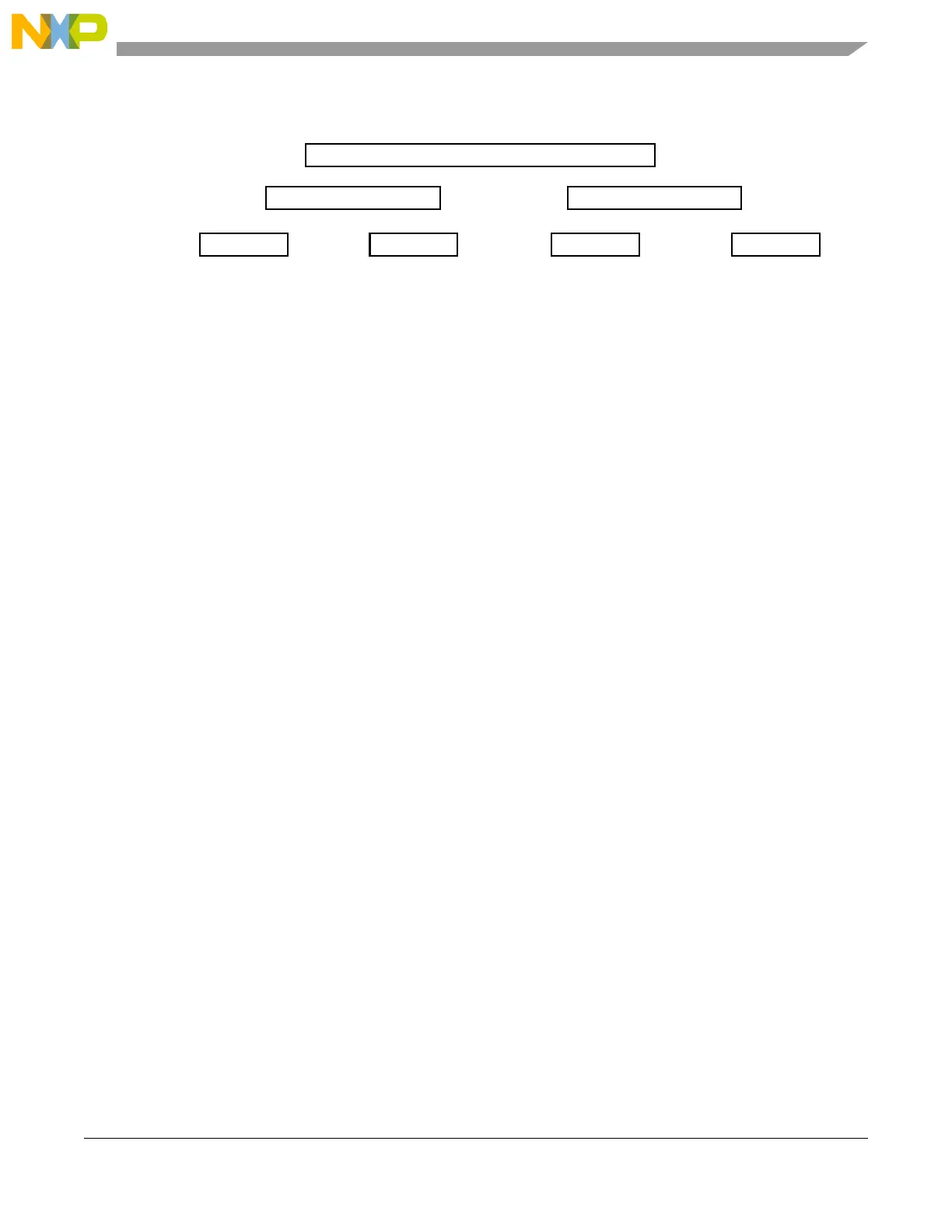

Figure 19-15. Data Port example arrangement showing configuration for different port width accesses

The SIUL has separate data input (GPDIn_n, see Section 19.5.3.11, “GPIO Pad Data Input Registers

(GPDI0_3–GPDI120_123)) and data output (GPDOn_n, see Section 19.5.3.10, “GPIO Pad Data Output

Registers (GPDO0_3–GPDO120_123)) registers for all pads, allowing the possibility of reading back an

input or output value of a pad directly. This supports the ability to validate what is present on the pad rather

than simply confirming the value that was written to the data register by accessing the data input registers.

Data output registers allow an output pad to be driven high or low (with the option of push-pull or open

drain drive). Input registers are read-only and reflect the respective pad value.

When the pad is configured to use one of its alternate functions, the data input value reflects the respective

value of the pad. If a write operation is performed to the data output register for a pad configured as an

alternate function (non-GPIO), this write will not be reflected by the pad value until reconfigured to GPIO.

The allocation of what input function is connected to the pin is defined by the PSMI registers (PCRn, see

Section 19.5.3.9, “Pad Selection for Multiplexed Inputs Registers (PSMI0_3–PSMI28_31)).”

19.6.3 External interrupts

The SIUL supports 16 external interrupts, EIRQ0–EIRQ15. In the signal description chapter of this

reference manual, mapping is shown for external interrupts to pads.

The SIUL supports twointerrupt vectors to the interrupt controller. Each vector interrupt has eight external

interrupts combined together with the presence of flag generating an interrupt for that vector if enabled.

All of the external interrupt pads within a single group have equal priority.

See Figure 19-16 for an overview of the external interrupt implementation.

31

23

SIUL Base+ 0x0C00

15 7 0

SIUL Base+

15 7 0

SIUL Base+

15 7 0

SIUL Base+

70

0x0C03

SIUL Base+

70

0x0C02

SIUL Base+

70

0x0C01

SIUL Base+

70

0x0C00

0x0C02 0x0C00

32-bit Access (2 ports)

16-bit Access (full port) 16-bit Access (full port)

8-bit Access

(half port)

8-bit Access

(half port)

8-bit Access

(half port)

8-bit Access

(half port)

Loading...

Loading...