MPC5604B/C Microcontroller Reference Manual, Rev. 8

Freescale Semiconductor 607

25.4.2 Control logic registers

25.4.2.1 Main Configuration Register (MCR)

The Main Configuration Register (MCR) provides configuration settings for the ADC.

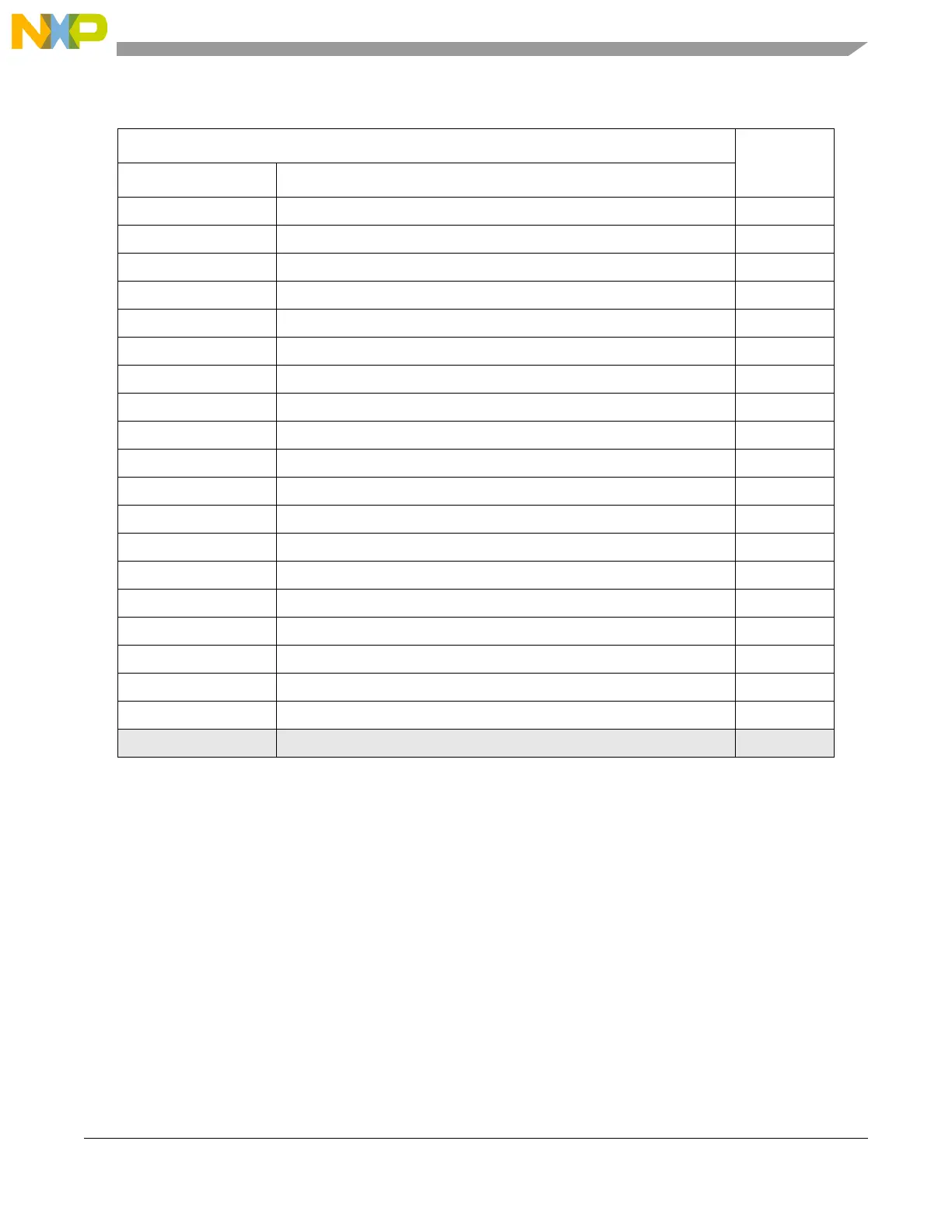

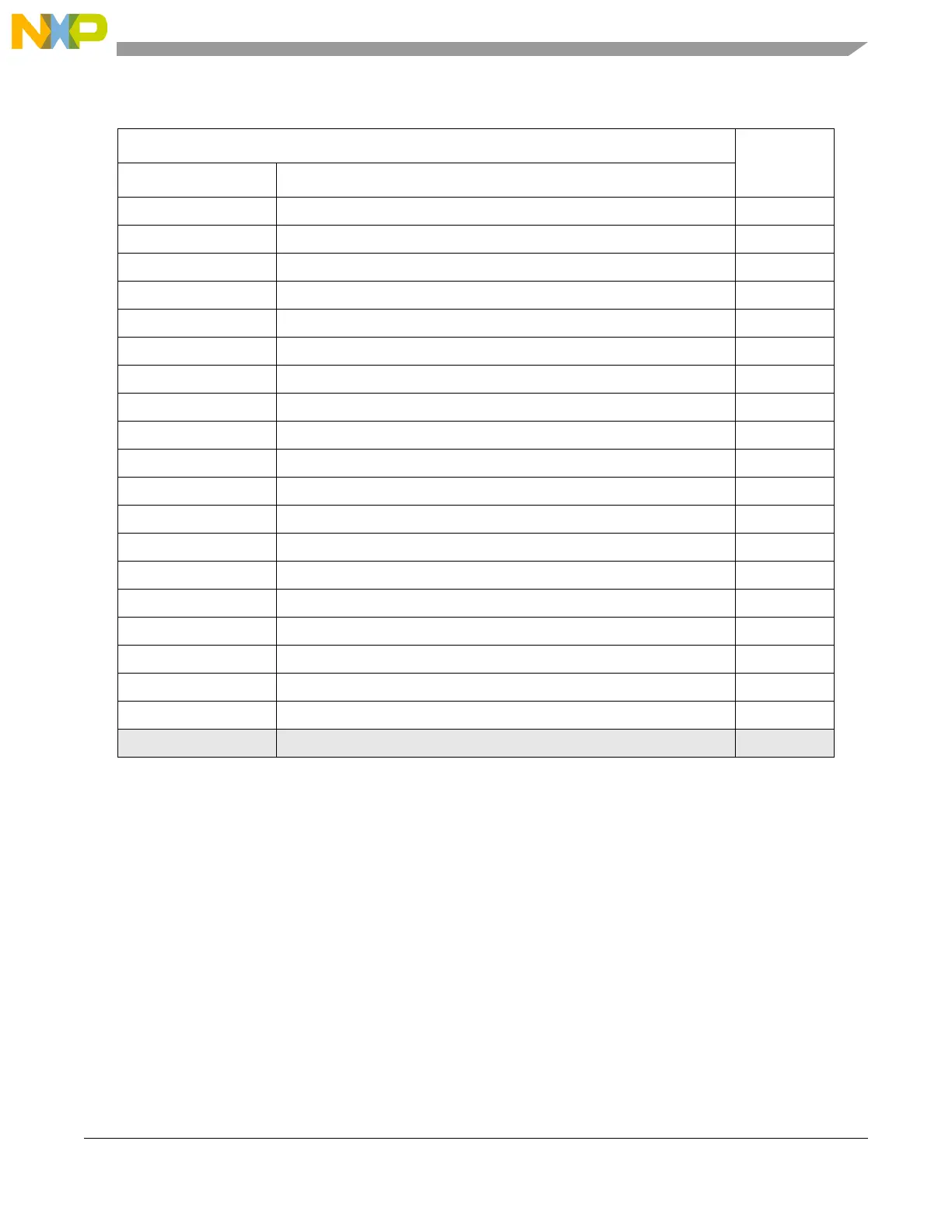

0x0234 Channel 77 Data Register (CDR77) on page 628

0x0238 Channel 78 Data Register (CDR78) on page 628

0x023C Channel 79 Data Register (CDR79) on page 628

0x0240 Channel 80 Data Register (CDR80) on page 628

0x0244 Channel 81 Data Register (CDR81) on page 628

0x0248 Channel 82 Data Register (CDR82) on page 628

0x024C Channel 83 Data Register (CDR83) on page 628

0x0250 Channel 84 Data Register (CDR84) on page 628

0x0254 Channel 85 Data Register (CDR85) on page 628

0x0258 Channel 86 Data Register (CDR86) on page 628

0x025C Channel 87 Data Register (CDR87) on page 628

0x0260 Channel 88 Data Register (CDR88) on page 628

0x0264 Channel 89 Data Register (CDR89) on page 628

0x0268 Channel 90 Data Register (CDR90) on page 628

0x026C Channel 91 Data Register (CDR91) on page 628

0x0270 Channel 92 Data Register (CDR92) on page 628

0x0274 Channel 93 Data Register (CDR93) on page 628

0x0278 Channel 94 Data Register (CDR94) on page 628

0x027C Channel 95 Data Register (CDR95) on page 628

0x0280 .. 0x02FF Reserved —

Table 25-6. ADC_0 digital registers (continued)

Base address: 0xFFE0_0000

Location

Address offset Register name

Loading...

Loading...