MPC5604B/C Microcontroller Reference Manual, Rev. 8

Freescale Semiconductor 233

12.4.3 NMI Configuration Register (NCR)

This register holds the configuration bits for the non-maskable interrupt settings.

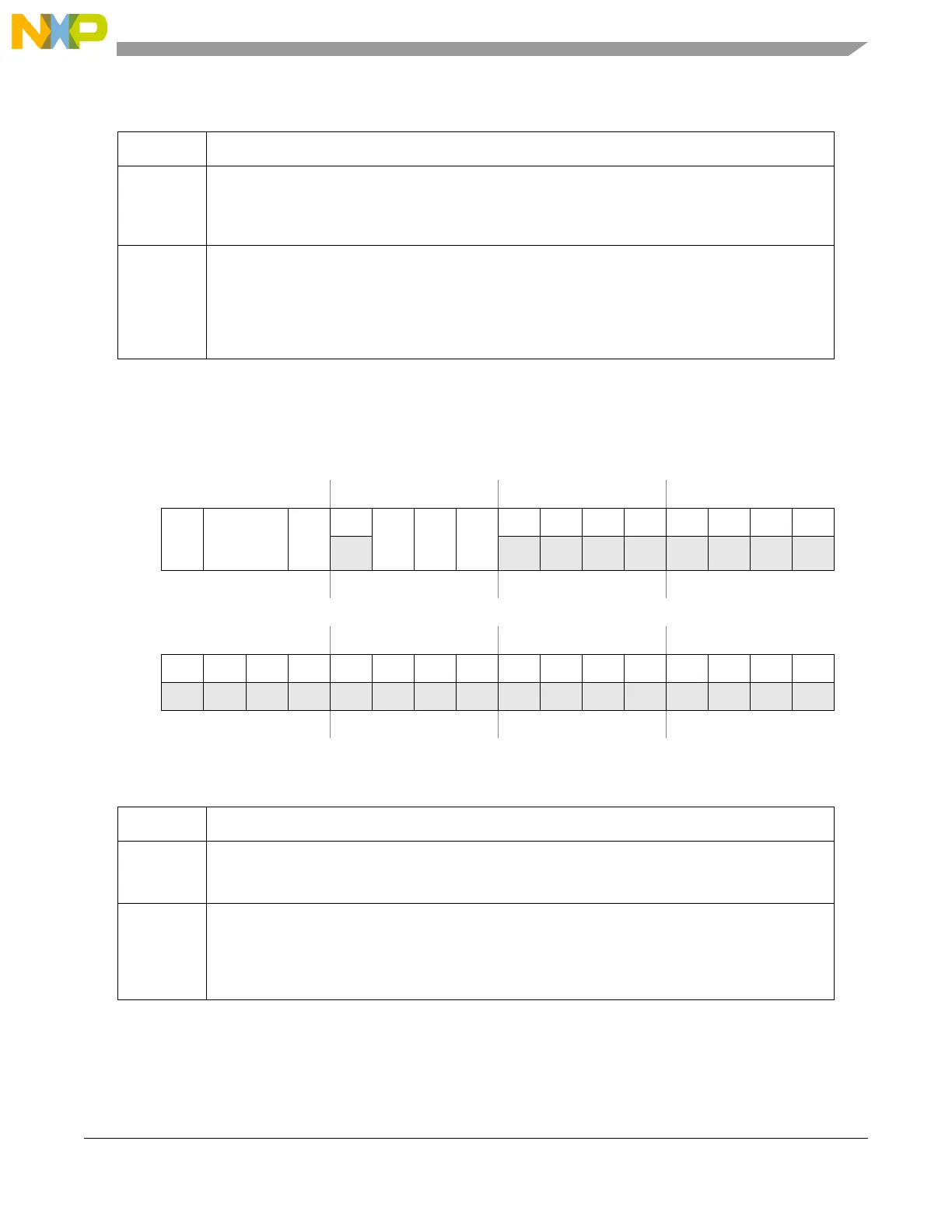

Table 12-3. NSR field descriptions

Field Description

NIF0 NMI Status Flag

If enabled (NREE0 or NFEE0 set), NIF0 causes an interrupt request.

1 An event as defined by NREE0 and NFEE0 has occurred

0 No event has occurred on the pad

NOVF0 NMI Overrun Status Flag

It will be a copy of the current NIF0 value whenever an NMI event occurs, thereby indicating to the

software that an NMI occurred while the last one was not yet serviced. If enabled (NREE0 or NFEE0

set), NOVF0 causes an interrupt request.

1 An overrun has occurred on NMI input

0 No overrun has occurred on NMI input

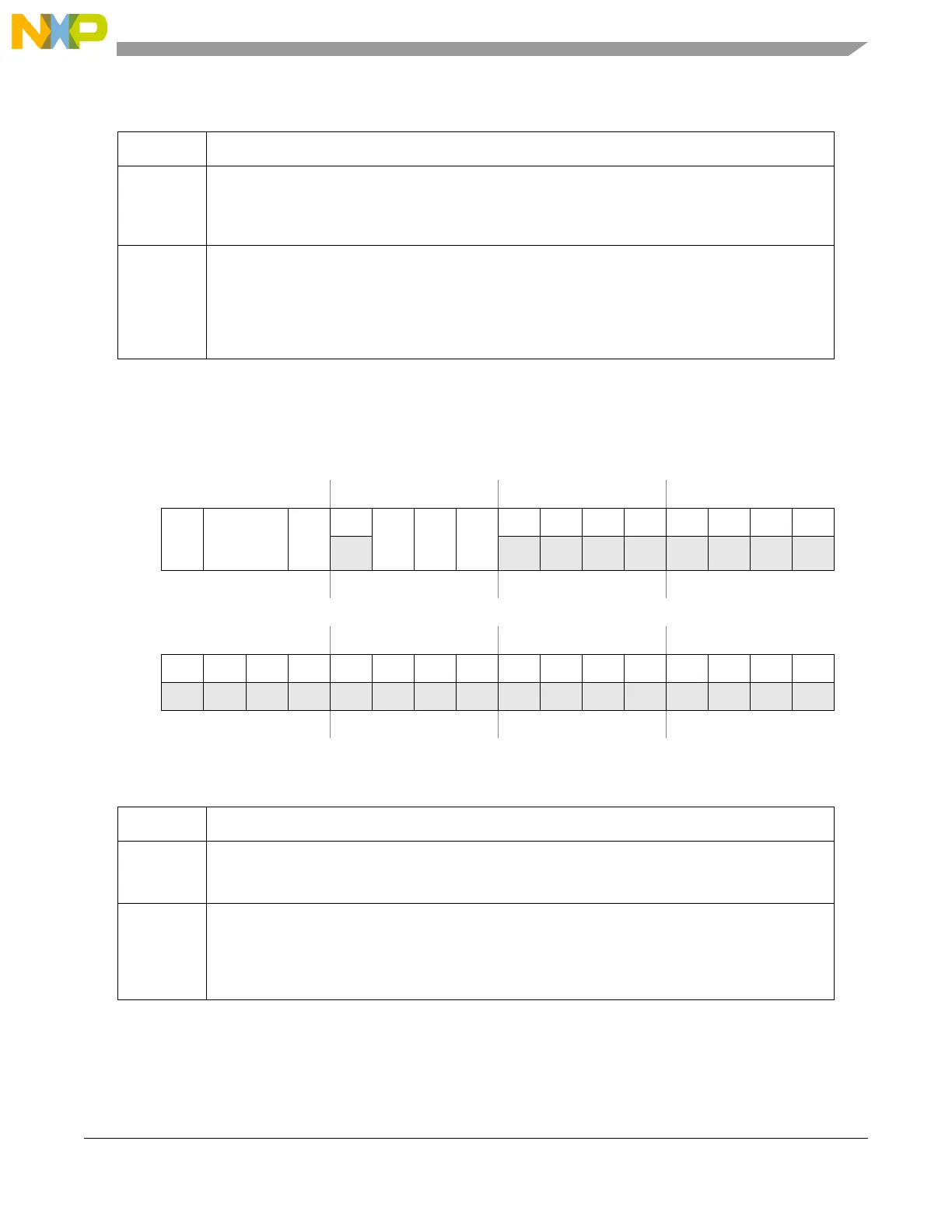

Offset: 0x08 Access: User read/write

0123456789101112131415

R

NLOCK0

NDSS0

NWRE0

0

NREE0

NFEE0

NFE0

00000000

W

Reset0000000000000000

16 17 18 19 20 21 22 23 24 25 26 27 28 29 30 31

R0000000000000000

W

Reset0000000000000000

Figure 12-3. NMI Configuration Register (NCR)

Table 12-4. NCR field descriptions

Field Description

NLOCK0 NMI Configuration Lock Register

Writing a 1 to this bit locks the configuration for the NMI until it is unlocked by a system reset. Writing

a 0 has no effect.

NDSS0 NMI Destination Source Select

00 Non-maskable interrupt

01 Critical interrupt

10 Machine check request

11 Reserved—no NMI, critical interrupt, or machine check request generated

Loading...

Loading...