MPC5604B/C Microcontroller Reference Manual, Rev. 8

Freescale Semiconductor 235

NOTE

Status bits associated with on-chip wakeup sources are located to the left of

the external wakeup/interrupt status bits and are read only. The wakeup for

these sources must be configured and cleared at the on-chip wakeup source.

Also, the configuration registers for the external interrupts/wakeups do not

have corresponding bits.

12.4.5 Interrupt Request Enable Register (IRER)

This register is used to enable the interrupt messaging from the wakeup/interrupt pads to the interrupt

controller.

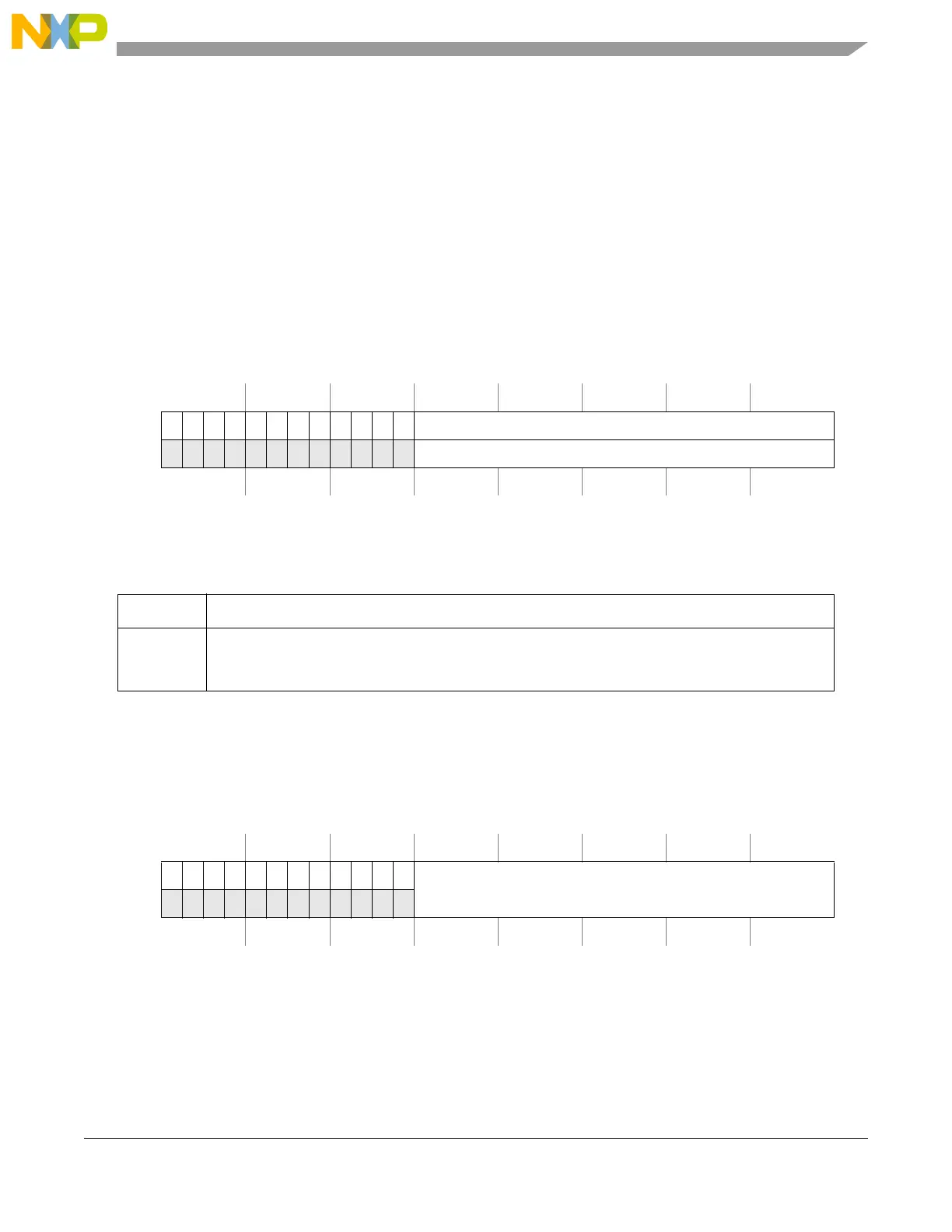

12.4.6 Wakeup Request Enable Register (WRER)

This register is used to enable the system wakeup messaging from the wakeup/interrupt pads to the mode

entry and power control modules.

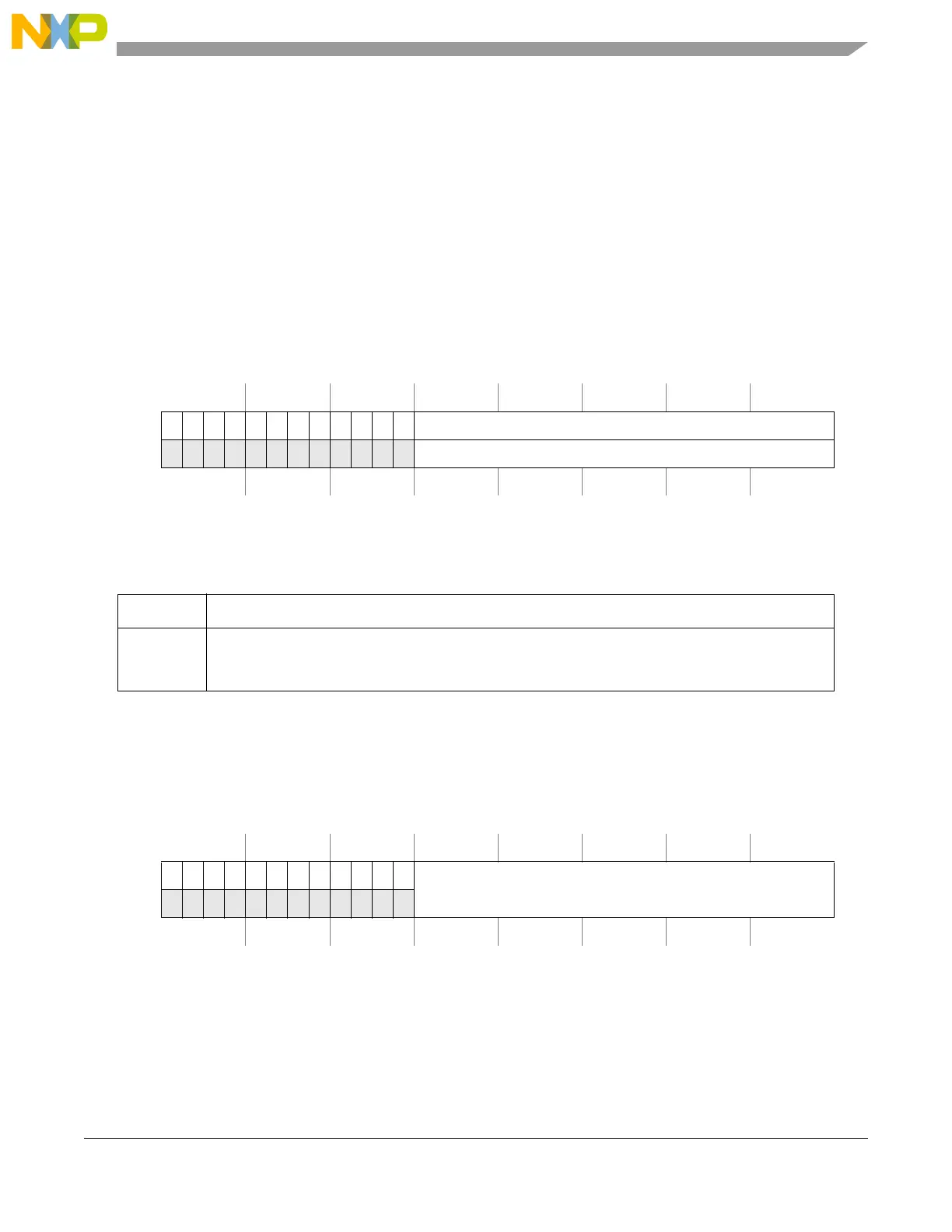

Offset: 0x18 Access: User read/write

012345678910111213141516171819202122232425262728293031

R000000000000 EIRE[19:0]

1

1

EIRE[18:15] are not available in all 100-pin packages.

W

w1c

Reset00000000000000000000000000000000

Figure 12-5. Interrupt Request Enable Register (IRER)

Table 12-6. IRER field descriptions

Field Description

EIRE[x] External Interrupt Request Enable x

1 A set EIF[x] bit causes an interrupt request

0 Interrupt requests from the corresponding EIF[x] bit are disabled

Offset: 0x1C Access: User read/write

012345678910111213141516171819202122232425262728293031

R000000000000

WRE[19:0]

1

1

WRE[18:15] are not available in all 100-pin packages.

W

Reset00000000000000000000000000000000

Figure 12-6. Wakeup Request Enable Register (WRER)

Loading...

Loading...