MPC5604B/C Microcontroller Reference Manual, Rev. 8

164 Freescale Semiconductor

8.3.1.22 Peripheral Control Registers (ME_PCTL0…143)

These registers select the configurations during run and non-run modes for each peripheral.

Table 8-14. Low-Power Peripheral Configuration Registers (ME_LP_PC0…7) Field Descriptions

Field Description

STANDBY Peripheral control during STANDBY

0 Peripheral is frozen with clock gated

1 Peripheral is active

STOP Peripheral control during STOP

0 Peripheral is frozen with clock gated

1 Peripheral is active

HALT Peripheral control during HALT

0 Peripheral is frozen with clock gated

1 Peripheral is active

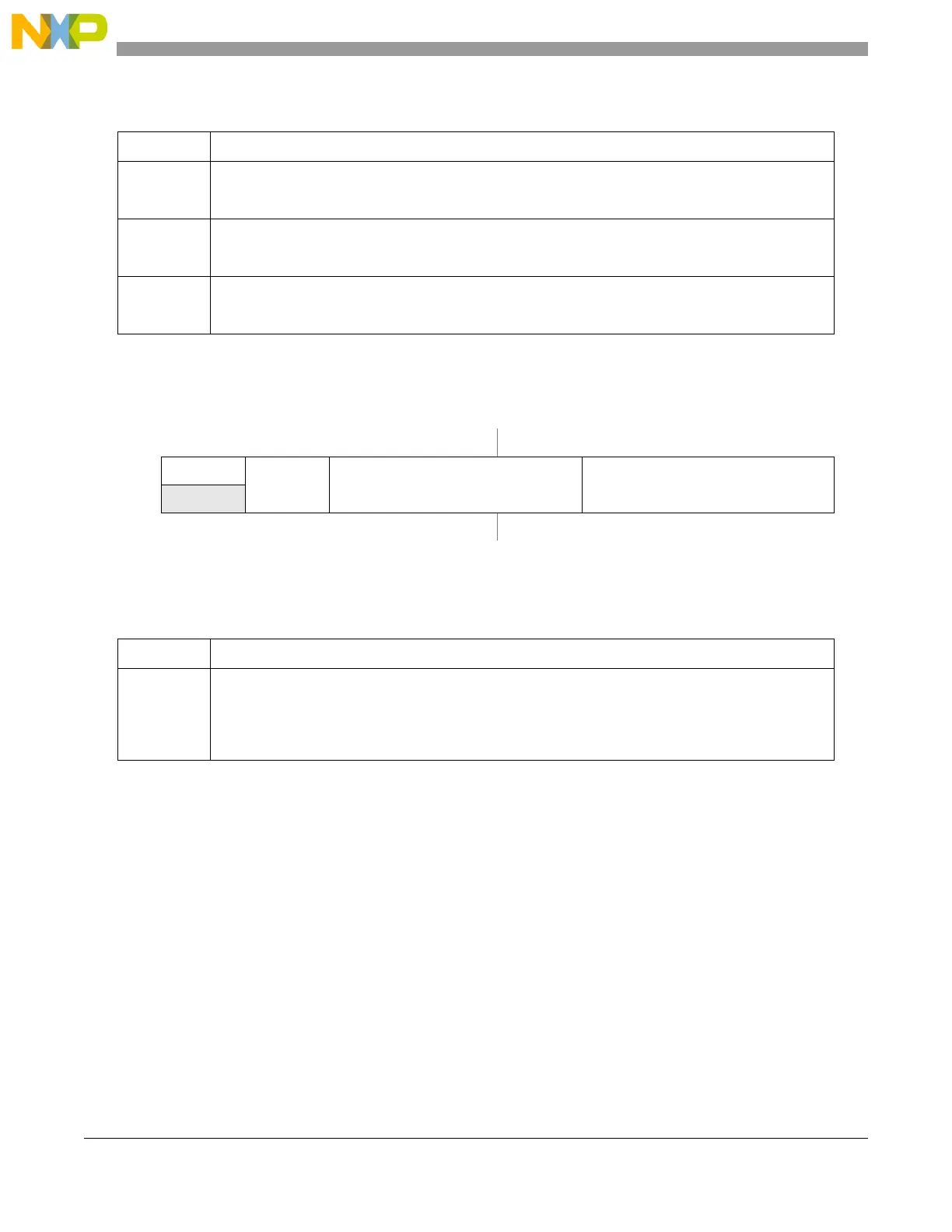

Address 0xC3FD_C0C0 - 0xC3FD_C14F Access: Supervisor read/write

01234567

R 0

DBG_F LP_CFG RUN_CFG

W

Reset00000000

Figure 8-23. Peripheral Control Registers (ME_PCTL0…143)

Table 8-15. Peripheral Control Registers (ME_PCTL0…143) Field Descriptions

Field Description

DBG_F Peripheral control in debug mode — This bit controls the state of the peripheral in debug mode.

0 Peripheral state depends on RUN_CFG/LP_CFG bits and the device mode.

1 Peripheral is frozen if not already frozen in device modes.

Note: This feature is useful to freeze the peripheral state while entering debug. For example, this may

be used to prevent a reference timer from running while making a debug accesses.

Loading...

Loading...