MPC5604B/C Microcontroller Reference Manual, Rev. 8

Freescale Semiconductor 163

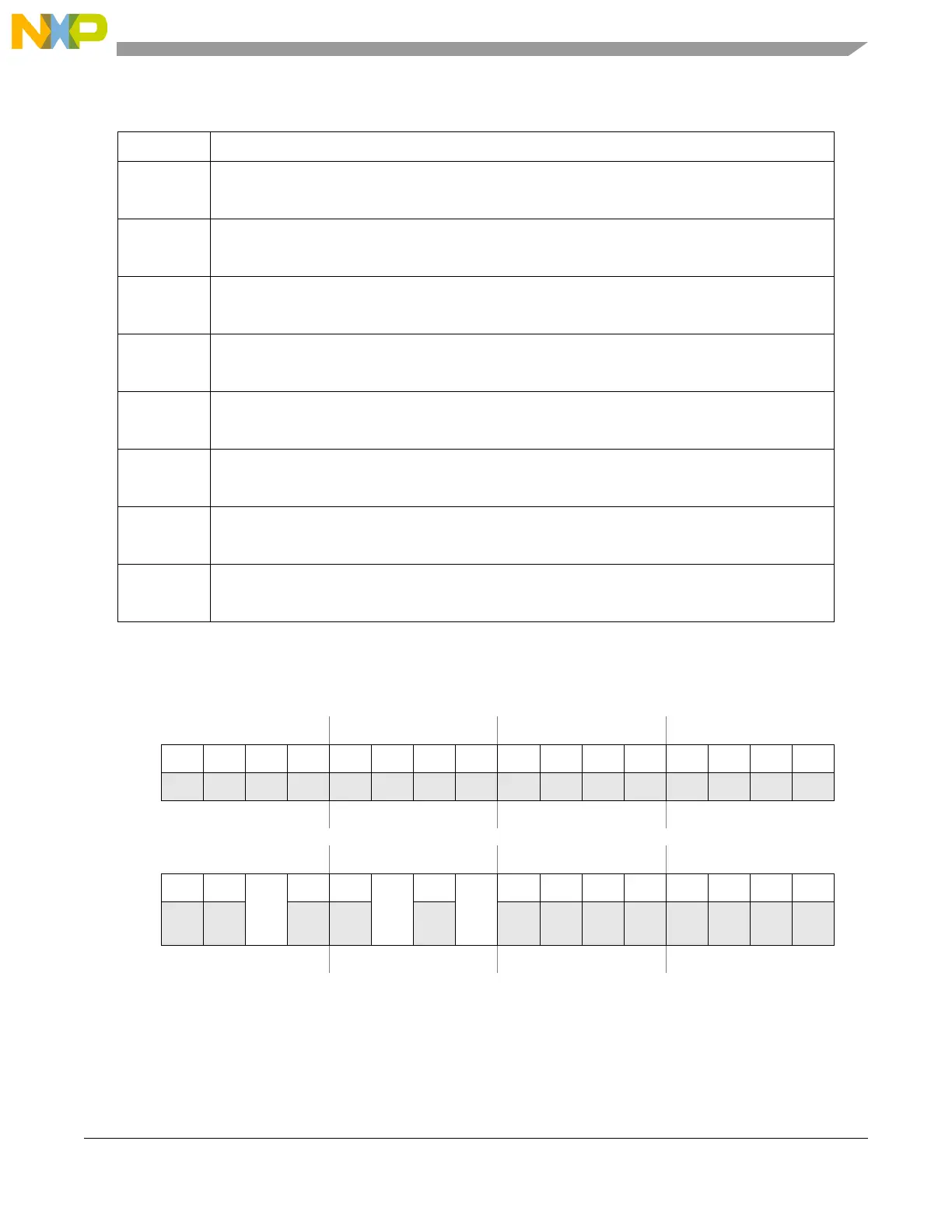

8.3.1.21 Low-Power Peripheral Configuration Registers (ME_LP_PC0…7)

These registers configure eight different types of peripheral behavior during non-run modes.

Table 8-13. Run Peripheral Configuration Registers (ME_RUN_PC0…7) Field Descriptions

Field Description

RUN3 Peripheral control during RUN3

0 Peripheral is frozen with clock gated

1 Peripheral is active

RUN2 Peripheral control during RUN2

0 Peripheral is frozen with clock gated

1 Peripheral is active

RUN1 Peripheral control during RUN1

0 Peripheral is frozen with clock gated

1 Peripheral is active

RUN0 Peripheral control during RUN0

0 Peripheral is frozen with clock gated

1 Peripheral is active

DRUN Peripheral control during DRUN

0 Peripheral is frozen with clock gated

1 Peripheral is active

SAFE Peripheral control during SAFE

0 Peripheral is frozen with clock gated

1 Peripheral is active

TEST Peripheral control during TEST

0 Peripheral is frozen with clock gated

1 Peripheral is active

RESET Peripheral control during RESET

0 Peripheral is frozen with clock gated

1 Peripheral is active

Address 0xC3FD_C0A0 - 0xC3FD_C0BC Access: Supervisor read/write

0123456789101112131415

R0000000000000000

W

Reset0000000000000000

16 17 18 19 20 21 22 23 24 25 26 27 28 29 30 31

R0 0

STANDBY

00

STOP

0

HALT

00000000

W

Reset0000000000000000

Figure 8-22. Low-Power Peripheral Configuration Registers (ME_LP_PC0…7)

Loading...

Loading...