MPC5604B/C Microcontroller Reference Manual, Rev. 8

780 Freescale Semiconductor

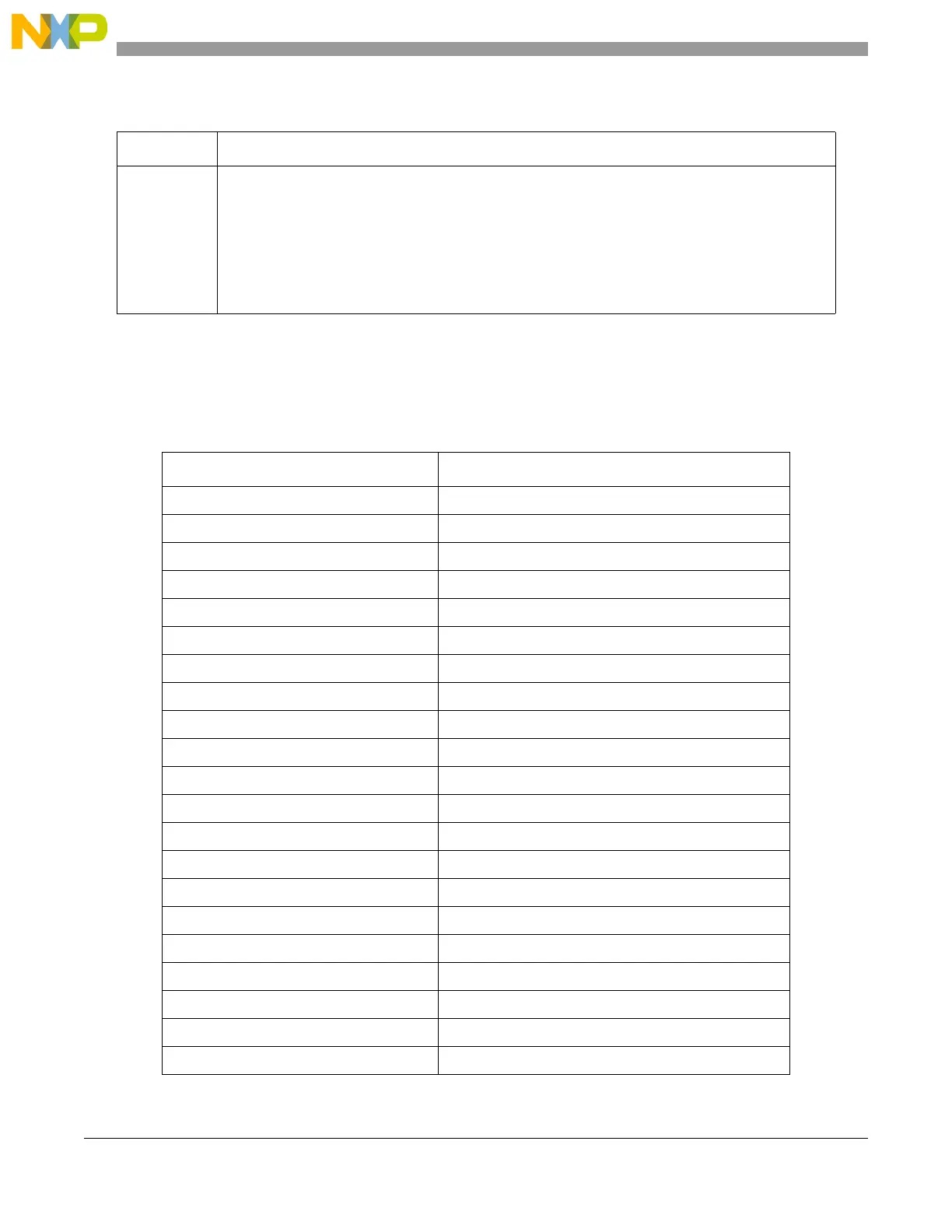

Table 31-17 associates the upper 7 bits of the ECC syndrome with the exact data bit in error for single-bit

correctable codewords. This table follows the bit vectoring notation where the LSB = 0. Note that the

syndrome value of 0x01 implies no error condition but this value is not readable when the PRESR is read

for the no error case.

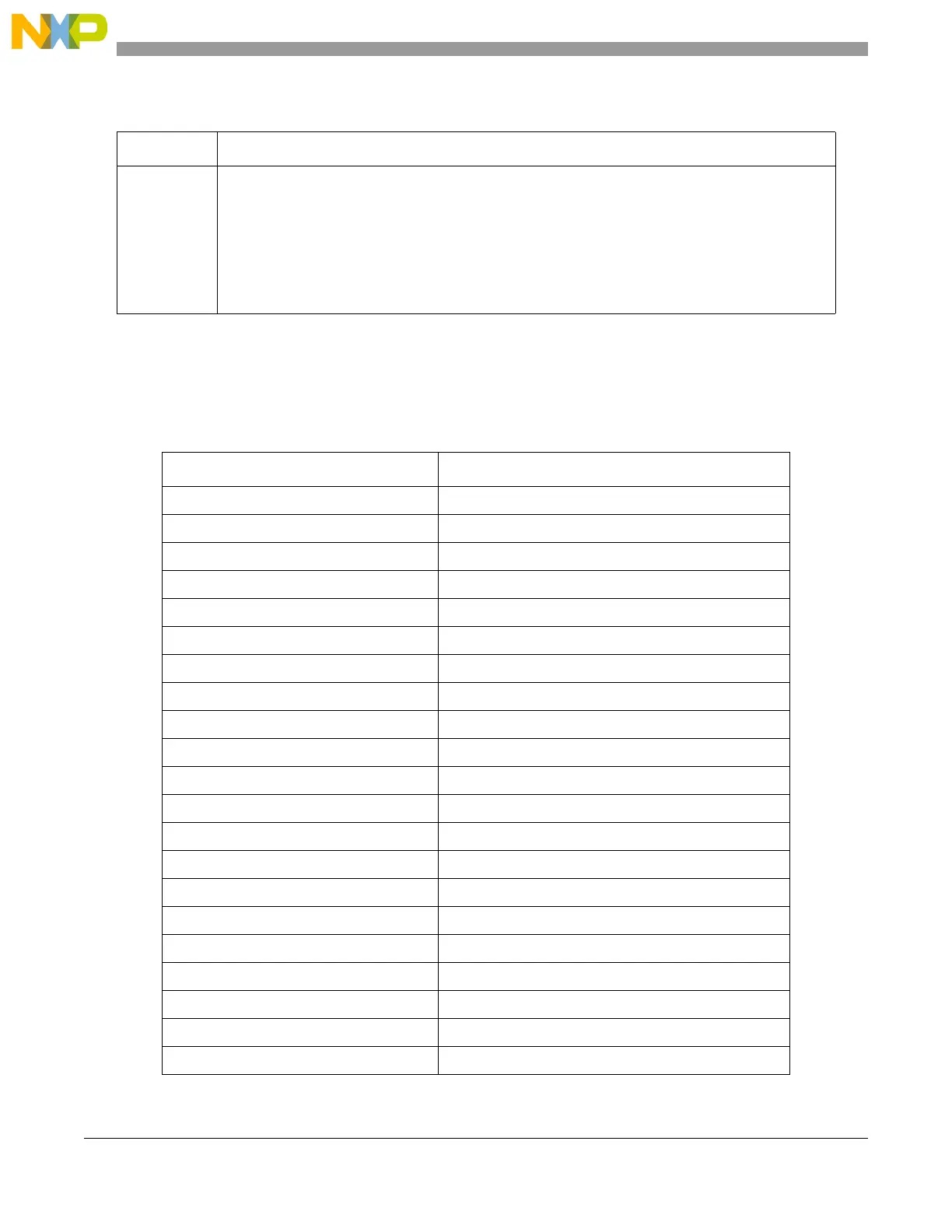

Table 31-16. PRESR field descriptions

Field Description

RESR SRAM ECC Syndrome Register

This 8-bit syndrome field includes 6 bits of Hamming decoded parity plus an odd-parity bit for the

entire 39-bit (32-bit data + 7 ECC) code word. The upper 7 bits of the syndrome specify the exact bit

position in error for single-bit correctable codewords, and the combination of a non-zero 7-bit

syndrome plus overall incorrect parity bit signal a multi-bit, non-correctable error.

For correctable single-bit errors, the mapping shown in Table 31-17 associates the upper 7 bits of

the syndrome with the data bit in error.

Table 31-17. RAM syndrome mapping for single-bit correctable errors

PRESR[RESR] Data bit in error

0x00 ECC ODD[0]

0x01 No error

0x02 ECC ODD[1]

0x04 ECC ODD[2]

0x06 DATA ODD BANK[31]

0x08 ECC ODD[3]

0x0a DATA ODD BANK[30]

0x0c DATA ODD BANK[29]

0x0e DATA ODD BANK[28]

0x10 ECC ODD[4]

0x12 DATA ODD BANK[27]

0x14 DATA ODD BANK[26]

0x16 DATA ODD BANK[25]

0x18 DATA ODD BANK[24]

0x1a DATA ODD BANK[23]

0x1c DATA ODD BANK[22]

0x50 DATA ODD BANK[21]

0x20 ECC ODD[5]

0x22 DATA ODD BANK[20]

0x24 DATA ODD BANK[19]

0x26 DATA ODD BANK[18]

Loading...

Loading...