MPC5604B/C Microcontroller Reference Manual, Rev. 8

Freescale Semiconductor 773

In the event that multiple status flags are signaled simultaneously, ECSM records the event with the R1BC

as highest priority, then F1BC, then RNCE, and finally FNCE.

31.4.2.7.3 ECC Error Generation Register (EEGR)

The ECC Error Generation Register is a 16-bit control register used to force the generation of single- and

double-bit data inversions in the memories with ECC, most notably the SRAM. This capability is provided

for two purposes:

• It provides a software-controlled mechanism for “injecting” errors into the memories during data

writes to verify the integrity of the ECC logic.

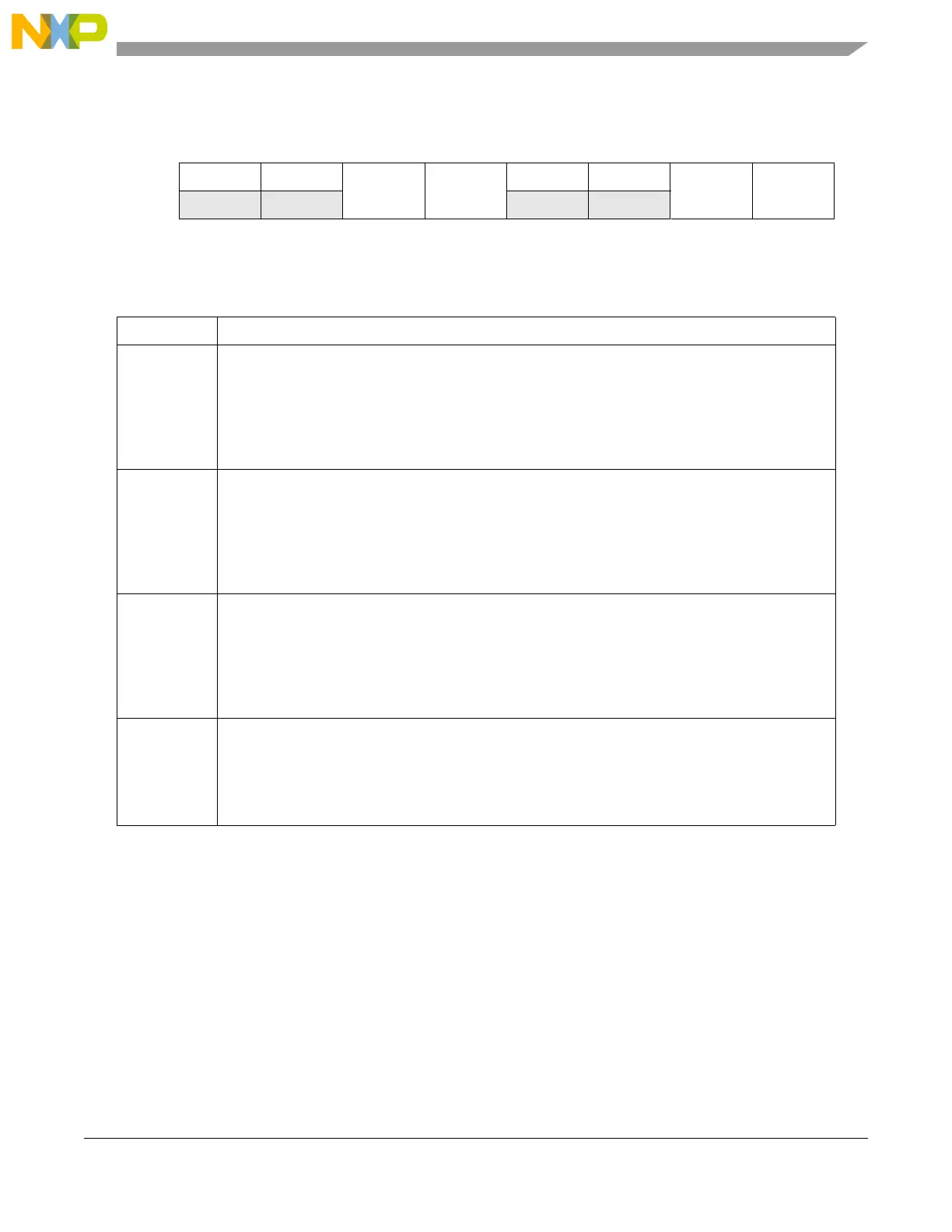

Offset: 0x47 Access: Read/write

01234567

R0 0

R1BC F1BC

00

RNCE FNCE

W

Reset:00000000

Figure 31-8. ECC Status Register (ESR)

Table 31-9. ESR field descriptions

Field Description

R1BC SRAM 1-bit Correction

This bit can only be set if ECR[EPR1BR] is asserted. The occurrence of a properly-enabled

single-bit SRAM correction generates a ECSM ECC interrupt request. The address, attributes and

data are also captured in the PREAR, PRESR, PREMR, PREAT and PREDR registers. To clear this

interrupt flag, write a 1 to this bit. Writing a 0 has no effect.

0 No reportable single-bit SRAM correction has been detected.

1 A reportable single-bit SRAM correction has been detected.

F1BC Flash Memory 1-bit Correction

This bit can only be set if ECR[EPF1BR] is asserted. The occurrence of a properly-enabled single-bit

flash memory correction generates a ECSM ECC interrupt request. The address, attributes and data

are also captured in the PFEAR, PFEMR, PFEAT and PFEDR registers. To clear this interrupt flag,

write a 1 to this bit. Writing a 0 has no effect.

0 No reportable single-bit flash memory correction has been detected.

1 A reportable single-bit flash memory correction has been detected.

RNCE SRAM Non-Correctable Error

The occurrence of a properly-enabled non-correctable SRAM error generates a ECSM ECC

interrupt request. The faulting address, attributes and data are also captured in the PREAR, PRESR,

PREMR, PREAT and PREDR registers. To clear this interrupt flag, write a 1 to this bit. Writing a 0

has no effect.

0 No reportable non-correctable SRAM error has been detected.

1 A reportable non-correctable SRAM error has been detected.

FNCE Flash Memory Non-Correctable Error

The occurrence of a properly-enabled non-correctable flash memory error generates a ECSM ECC

interrupt request. The faulting address, attributes and data are also captured in the PFEAR, PFEMR,

PFEAT and PFEDR registers. To clear this interrupt flag, write a 1 to this bit. Writing a 0 has no effect.

0 No reportable non-correctable flash memory error has been detected.

1 A reportable non-correctable flash memory error has been detected.

Loading...

Loading...