MPC5604B/C Microcontroller Reference Manual, Rev. 8

768 Freescale Semiconductor

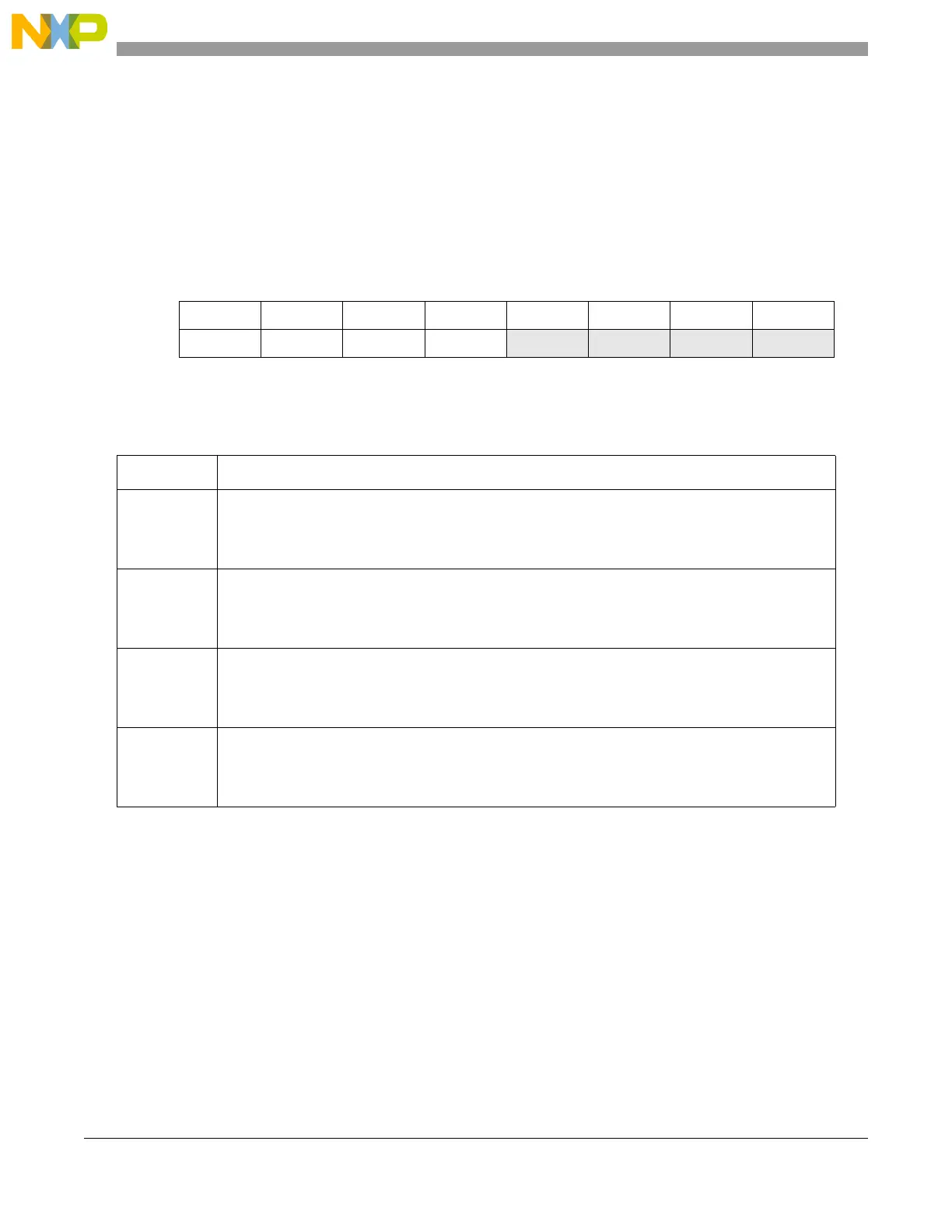

31.4.2.5 Miscellaneous Interrupt Register (MIR)

All interrupt requests associated with ECSM are collected in the MIR. This includes the processor core

system bus fault interrupt.

During the appropriate interrupt service routine handling these requests, the interrupt source contained in

the MIR must be explicitly cleared. See Figure 31-5 and Table 31-6.

Offset: 0x1F Access: Special

01234567

R FB0AI FB0SI FB1AI FB1SI 0 0 0 0

W1111

Reset:00000000

Figure 31-5. Miscellaneous Interrupt (MIR) Register

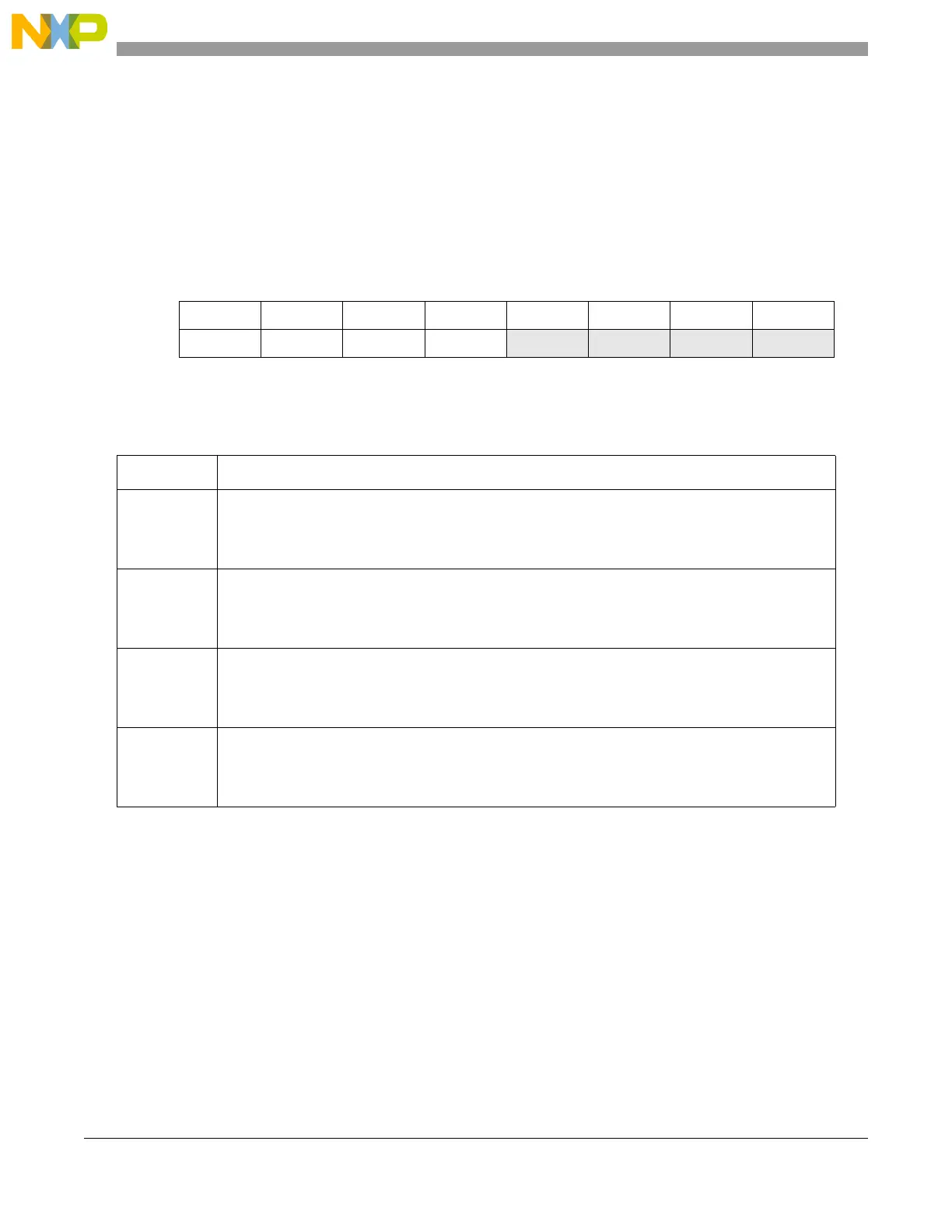

Table 31-6. MIR field descriptions

Field Description

FB0AI Flash Bank 0 Abort Interrupt

0 A flash bank 0 abort has not occurred.

1 A flash bank 0 abort has occurred. The interrupt request is negated by writing a 1 to this bit.

Writing a 0 has no effect.

FB0SI Flash Bank 0 Stall Interrupt

0 A flash bank 0 stall has not occurred.

1 A flash bank 0 stall has occurred. The interrupt request is negated by writing a 1 to this bit. Writing

a 0 has no effect.

FB1AI Flash Bank 1 Abort Interrupt

0 A flash bank 1 abort has not occurred.

1 A flash bank 1 abort has occurred. The interrupt request is negated by writing a 1 to this bit.

Writing a 0 has no effect.

FB1SI Flash Bank 1 Stall Interrupt

0 A flash bank 1 stall has not occurred.

1 A flash bank 1 stall has occurred. The interrupt request is negated by writing a 1 to this bit. Writing

a 0 has no effect.

Loading...

Loading...