MPC5604B/C Microcontroller Reference Manual, Rev. 8

Freescale Semiconductor 767

3. After entering the low-power mode, the interrupt controller enables a special combinational logic

path which evaluates all unmasked interrupt requests. The device remains in this mode until an

event which generates an unmasked interrupt request with a priority level greater than the value

programmed in the MWCR[PRILVL] occurs.

4. Once the appropriately-high interrupt request level arrives, the interrupt controller signals its

presence, and the ECSM responds by asserting an “exit_low_power_mode” signal.

5. The off-platform external logic senses the assertion of the “exit” signal, and re-enables the

appropriate clock signals.

6. With the processor core clocks enabled, the core handles the pending interrupt request.

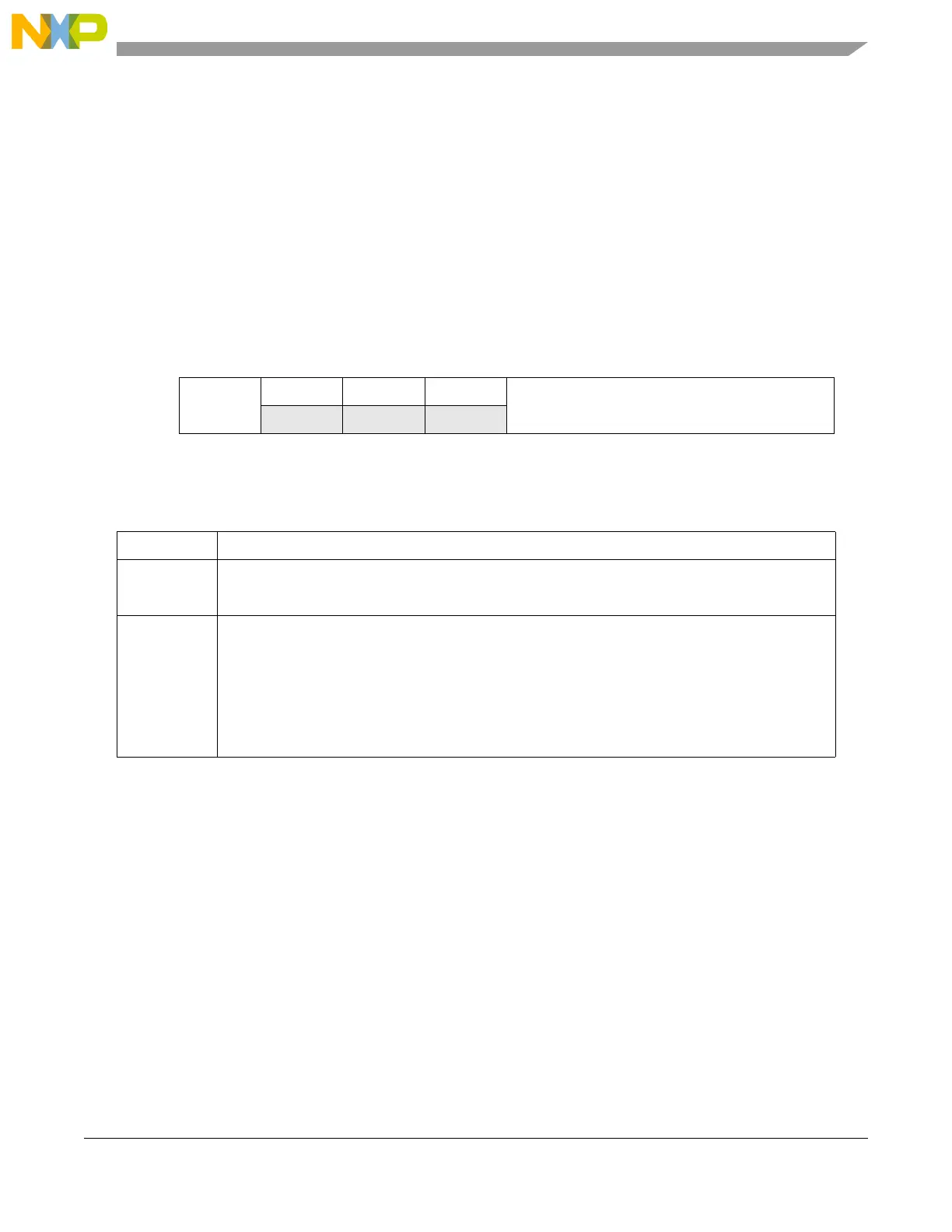

Offset: 0x13 Access: Read/write

01234567

R

ENBWCR

000

PRILVL

W

Reset:00000000

Figure 31-4. Miscellaneous Wakeup Control (MWCR) Register

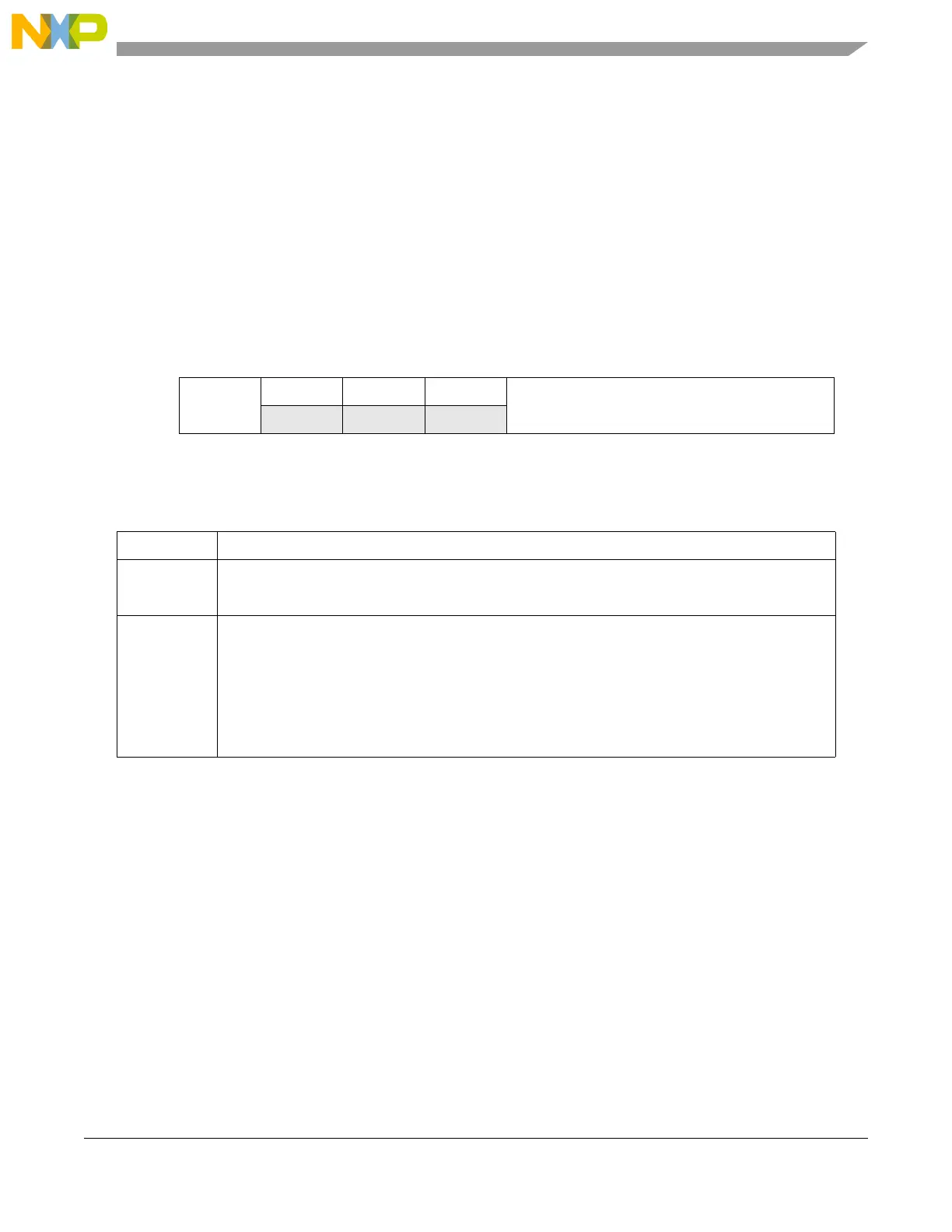

Table 31-5. MWCR field descriptions

Field Description

ENBWCR Enable WCR

0 MWCR is disabled.

1 MWCR is enabled.

PRILVL Interrupt Priority Level

The interrupt priority level is a core-specific definition. It specifies the interrupt priority level needed

to exit the low-power mode. Specifically, an unmasked interrupt request of a priority level greater

than the PRILVL value is required to exit the mode.

Certain interrupt controller implementations include logic associated with this priority level that

restricts the data value contained in this field to a [0, maximum - 1] range. See the specific interrupt

controller module for details.

Loading...

Loading...