MPC5604B/C Microcontroller Reference Manual, Rev. 8

Freescale Semiconductor 335

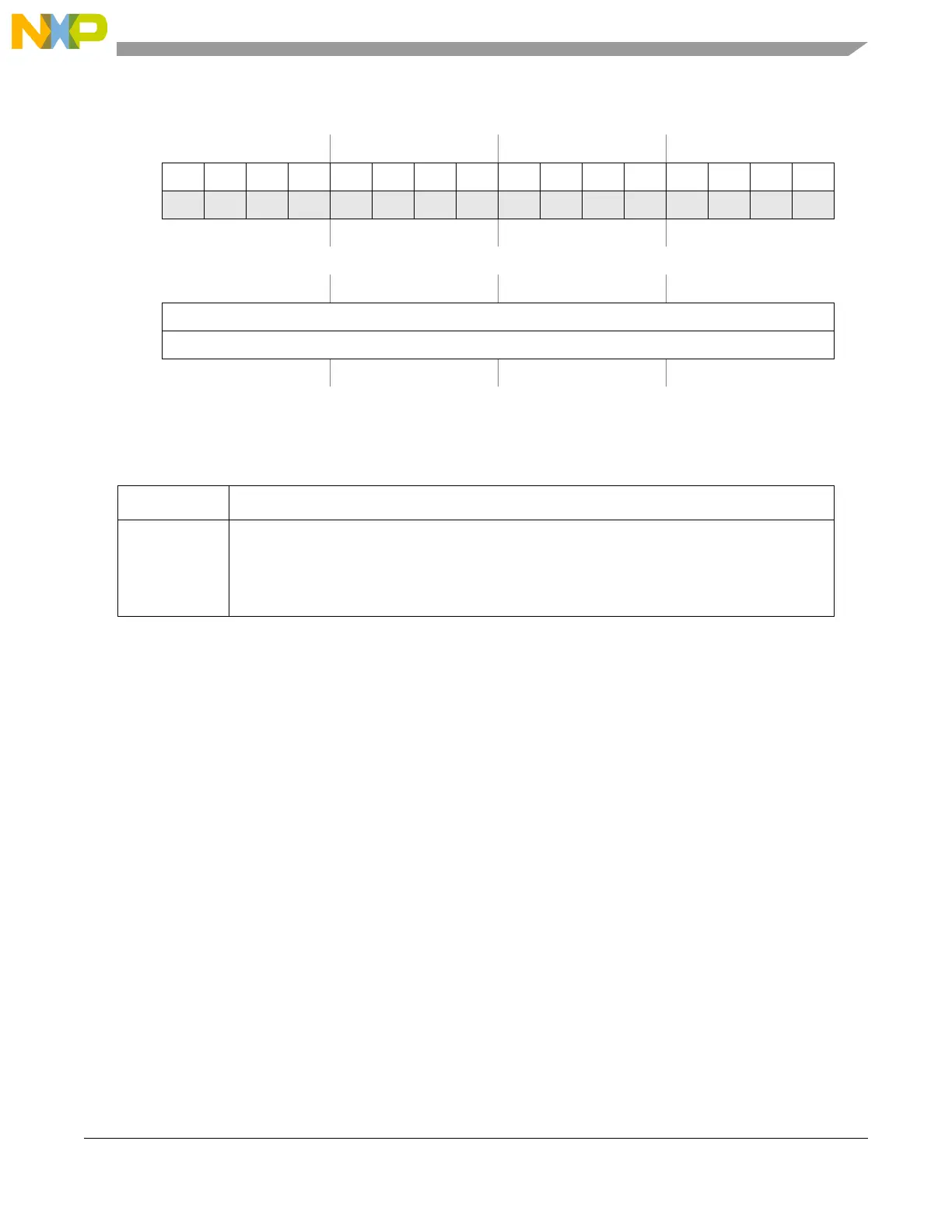

Offset: 0x0014 Access: User read/write

0123456789101112131415

R0000000000000000

W

Reset0000000000000000

16 17 18 19 20 21 22 23 24 25 26 27 28 29 30 31

R EIF[15:0]

1

1

EIF[15:0] in 144-pin LQFP and the 208 MAPBGA packages; EIF[11:0] in 100-pin LQFP package.

Ww1c

Reset0000000000000000

Figure 19-4. Interrupt Status Flag Register (ISR)

Table 19-5. ISR field descriptions

Field Description

EIF[x] External Interrupt Status Flag x

This flag can be cleared only by writing a ‘1’. Writing a ‘0’ has no effect. If enabled (IRER[x]), EIF[x]

causes an interrupt request.

0 No interrupt event has occurred on the pad

1 An interrupt event as defined by IREER[x] and IFEER[x] has occurred

Loading...

Loading...