MPC5604B/C Microcontroller Reference Manual, Rev. 8

Freescale Semiconductor 281

NOTE

The INTC has no spurious vector support. Therefore, if an asserted

peripheral or software settable interrupt request, whose PRIn value in

INTC_PSR0–INTC_PSR210 is higher than the PRI value in INTC_CPR,

negates before the interrupt request to the processor for that peripheral or

software settable interrupt request is acknowledged, the interrupt request to

the processor still can assert or will remain asserted for that peripheral or

software settable interrupt request. In this case, the interrupt vector will

correspond to that peripheral or software settable interrupt request. Also, the

PRI value in the INTC_CPR will be updated with the corresponding PRIn

value in INTC_PSRn. Furthermore, clearing the peripheral interrupt

request’s enable bit in the peripheral or, alternatively, setting its mask bit has

the same consequences as clearing its flag bit. Setting its enable bit or

clearing its mask bit while its flag bit is asserted has the same effect on the

INTC as an interrupt event setting the flag bit.

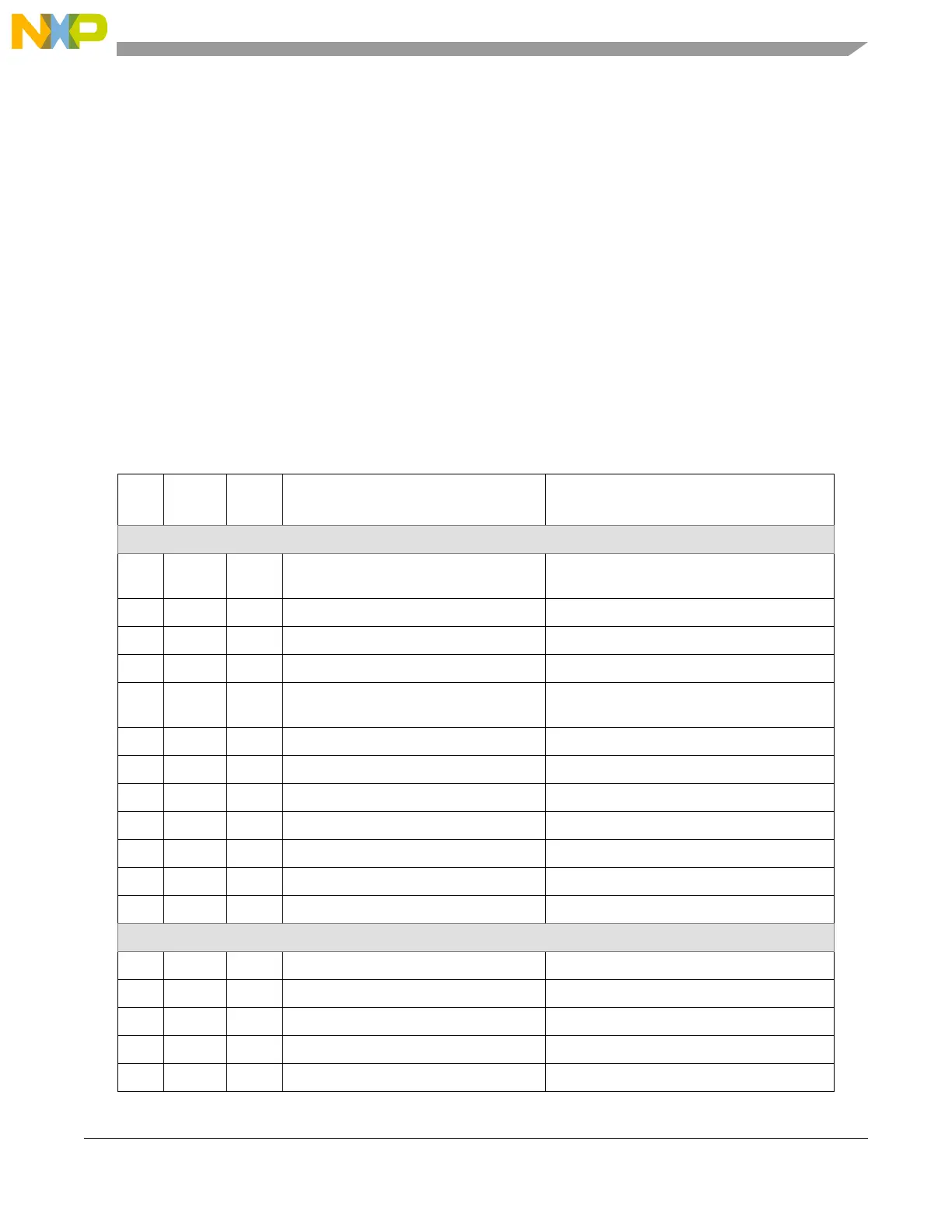

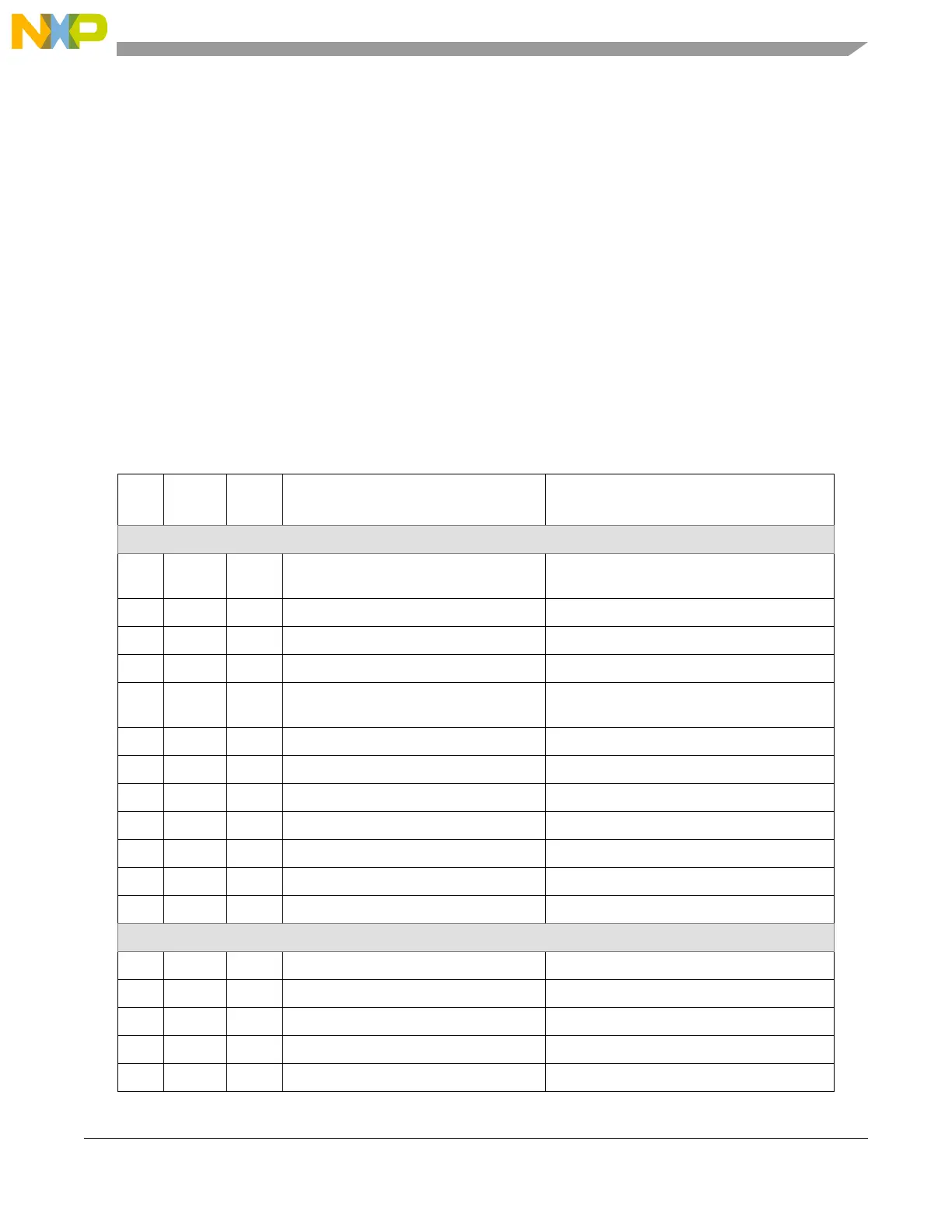

Table 16-10. Interrupt vector table

IRQ # Offset

Size

(bytes)

Interrupt Module

Section A (Core Section)

— 0x0000 16 Critical Input

(INTC software vector mode) / NMI

Core

— 0x0010 16 Machine check / NMI Core

— 0x0020 16 Data Storage Core

— 0x0030 16 Instruction Storage Core

— 0x0040 16 External Input

(INTC software vector mode)

Core

— 0x0050 16 Alignment Core

—0x0060 16Program Core

— 0x0070 16 Reserved Core

— 0x0080 16 System call Core

— 0x0090 96 Unused Core

— 0x00F0 16 Debug Core

— 0x0100 1792 Unused Core

Section B (On-Platform Peripherals)

0 0x0800 4 Software configurable flag 0 Software

1 0x0804 4 Software configurable flag 1 Software

2 0x0808 4 Software configurable flag 2 Software

3 0x080C 4 Software configurable flag 3 Software

4 0x0810 4 Software configurable flag 4 Software

Loading...

Loading...