MPC5604B/C Microcontroller Reference Manual, Rev. 8

Freescale Semiconductor 675

27.5.1.14 CFlash Nonvolatile Private Censorship Password 0 Register (NVPWD0)

The nonvolatile private censorship password 0 register contains the 32 LSB of the Password used to

validate the Censorship information contained in NVSCC0–1 registers.

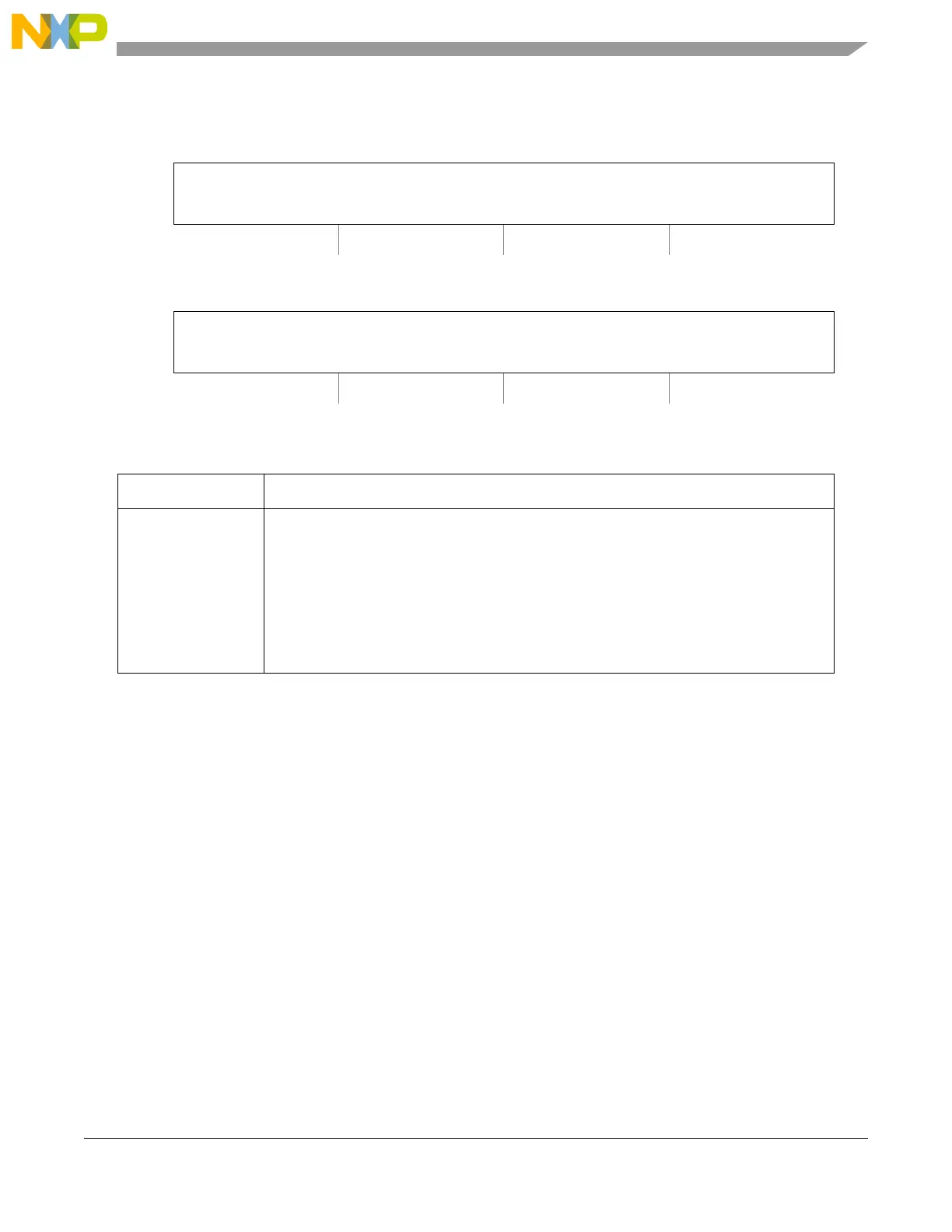

Offset: 0x00058 Access: Read/write

0 1 2 3 4 5 6 7 8 9 10 11 12 13 14 15

R

MS[159:144]

W

Reset

0000000000000000

16 17 18 19 20 21 22 23 24 25 26 27 28 29 30 31

R

MS[143:128]

W

Reset

0000000000000000

Figure 27-17. CFlash User Multiple Input Signature Register 4 (CFLASH_UMISR4)

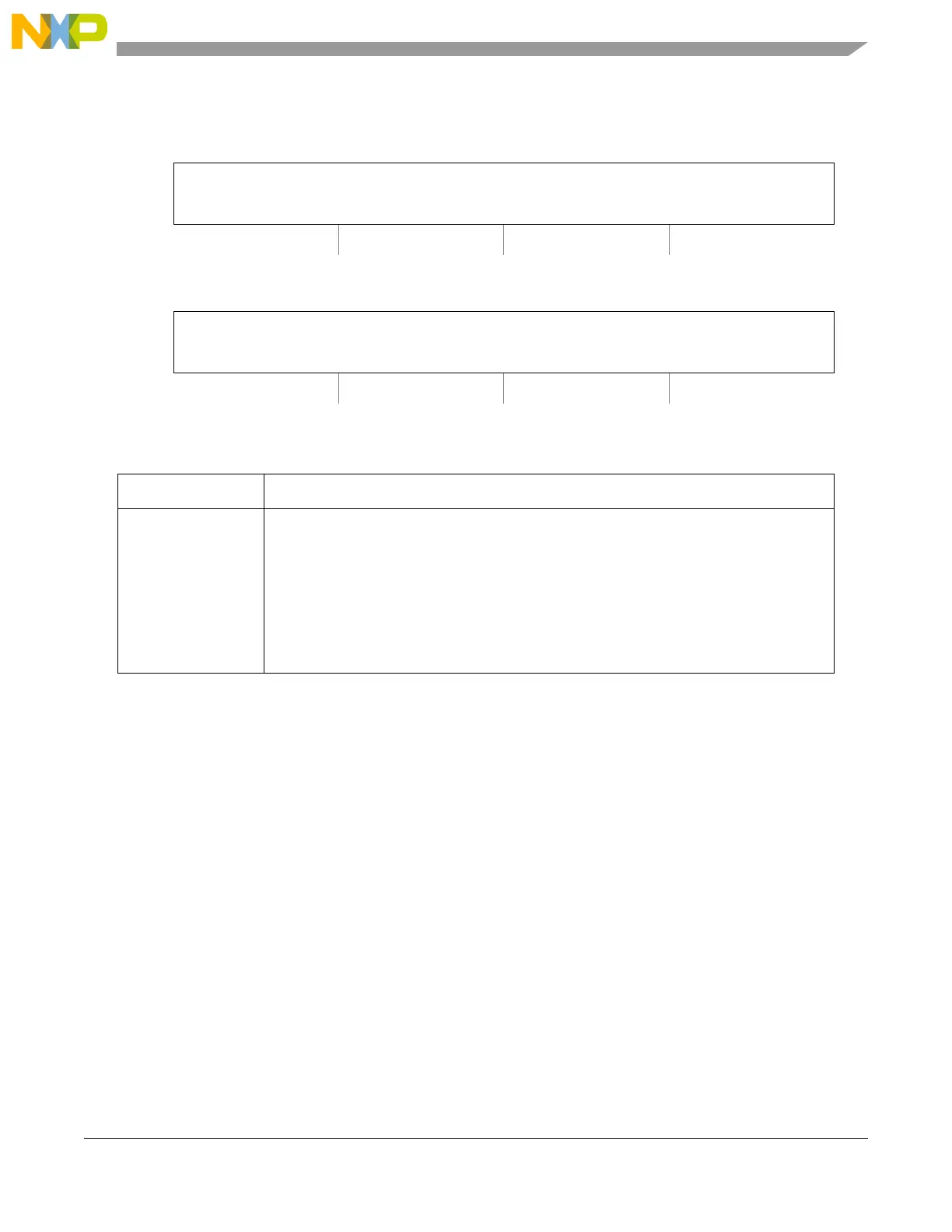

Table 27-28. CFLASH_UMISR4 field descriptions

Field Description

MS[159:128] Multiple input Signature, bits 159–128

These bits represent the MISR value obtained accumulating:

the 8 ECC bits for the even Double Word (on MS[135:128]);

the single ECC error detection for even Double Word (on MS138);

the double ECC error detection for even Double Word (on MS139);

the 8 ECC bits for the odd Double Word (on MS[151:144]);

the single ECC error detection for odd Double Word (on MS154);

the double ECC error detection for odd Double Word (on MS155).

The MS can be seeded to any value by writing the CFLASH_UMISR4 register.

Loading...

Loading...