USB on-the-go high-speed (OTG_HS) RM0090

1229/1422 Doc ID 018909 Rev 4

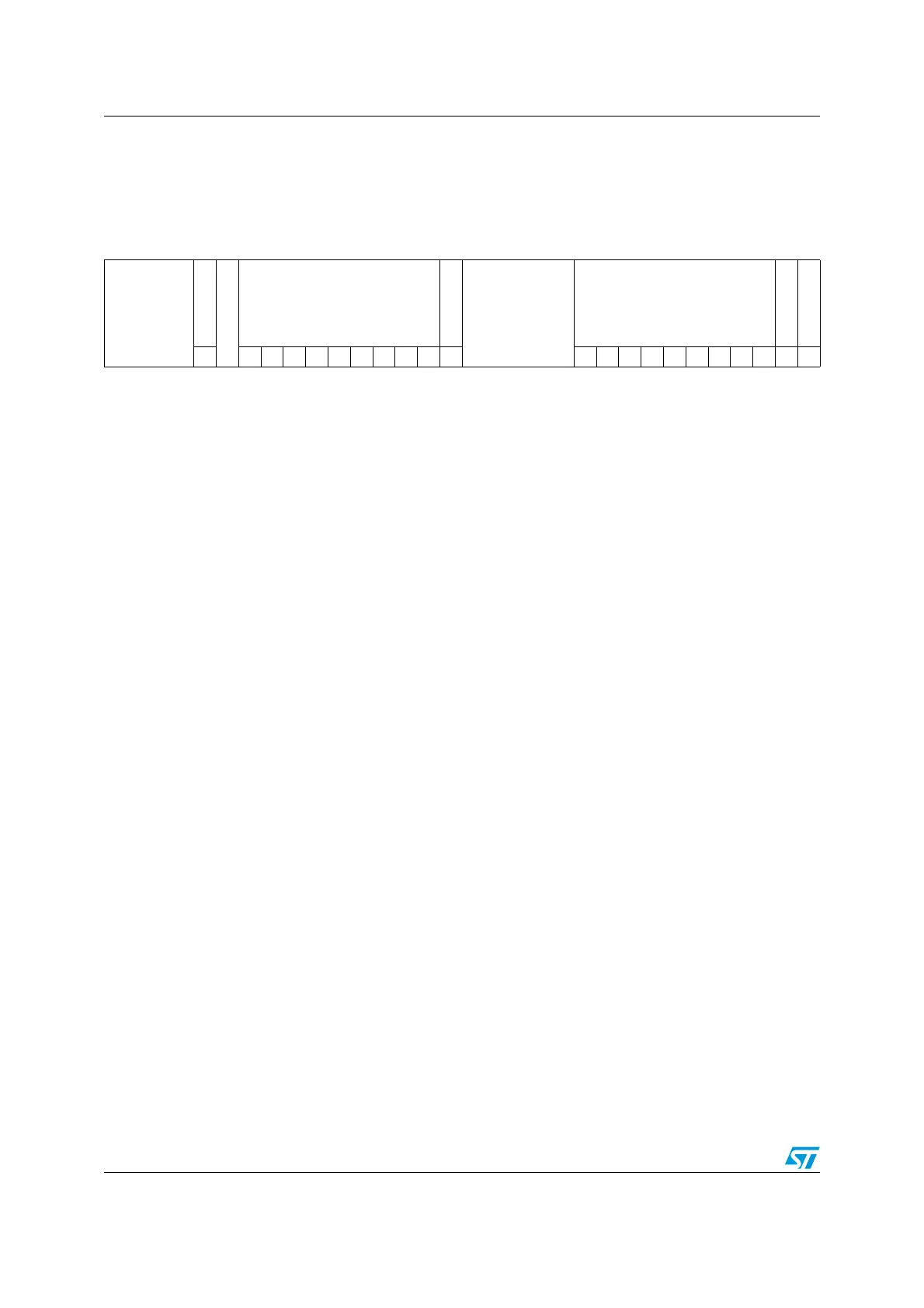

OTG_HS Device threshold control register (OTG_HS_DTHRCTL)

Address offset: 0x0830

Reset value: 0x0000 0000

313029282726252423222120191817161514131211109876543210

Reserved

ARPEN

Reserved

RXTHRLEN

RXTHREN

Reserved

TXTHRLEN

ISOTHREN

NONISOTHREN

rw rw rw rw rw rw rw rw rw rw rw rw rw rw rw rw rw rw rw rw rw rw

Bits 31:28 Reserved, must be kept at reset value.

Bit 27 ARPEN: Arbiter parking enable

This bit controls internal DMA arbiter parking for IN endpoints. When thresholding is enabled

and this bit is set to one, then the arbiter parks on the IN endpoint for which there is a token

received on the USB. This is done to avoid getting into underrun conditions. By default

parking is enabled.

Bit 26 Reserved, must be kept at reset value.

Bits 25: 17 RXTHRLEN: Receive threshold length

This field specifies the receive thresholding size in DWORDS. This field also specifies the

amount of data received on the USB before the core can start transmitting on the AHB. The

threshold length has to be at least eight DWORDS. The recommended value for RXTHRLEN

is to be the same as the programmed AHB burst length (HBSTLEN bit in

OTG_HS_GAHBCFG).

Bit 16 RXTHREN: Receive threshold enable

When this bit is set, the core enables thresholding in the receive direction.

Bits 15: 11 Reserved, must be kept at reset value.

Bits 10:2 TXTHRLEN: Transmit threshold length

This field specifies the transmit thresholding size in DWORDS. This field specifies the

amount of data in bytes to be in the corresponding endpoint transmit FIFO, before the core

can start transmitting on the USB. The threshold length has to be at least eight DWORDS.

This field controls both isochronous and nonisochronous IN endpoint thresholds. The

recommended value for TXTHRLEN is to be the same as the programmed AHB burst length

(HBSTLEN bit in OTG_HS_GAHBCFG).

Bit 1 ISOTHREN: ISO IN endpoint threshold enable

When this bit is set, the core enables thresholding for isochronous IN endpoints.

Bit 0 NONISOTHREN: Nonisochronous IN endpoints threshold enable

When this bit is set, the core enables thresholding for nonisochronous IN endpoints.

Loading...

Loading...