USB on-the-go high-speed (OTG_HS) RM0090

1233/1422 Doc ID 018909 Rev 4

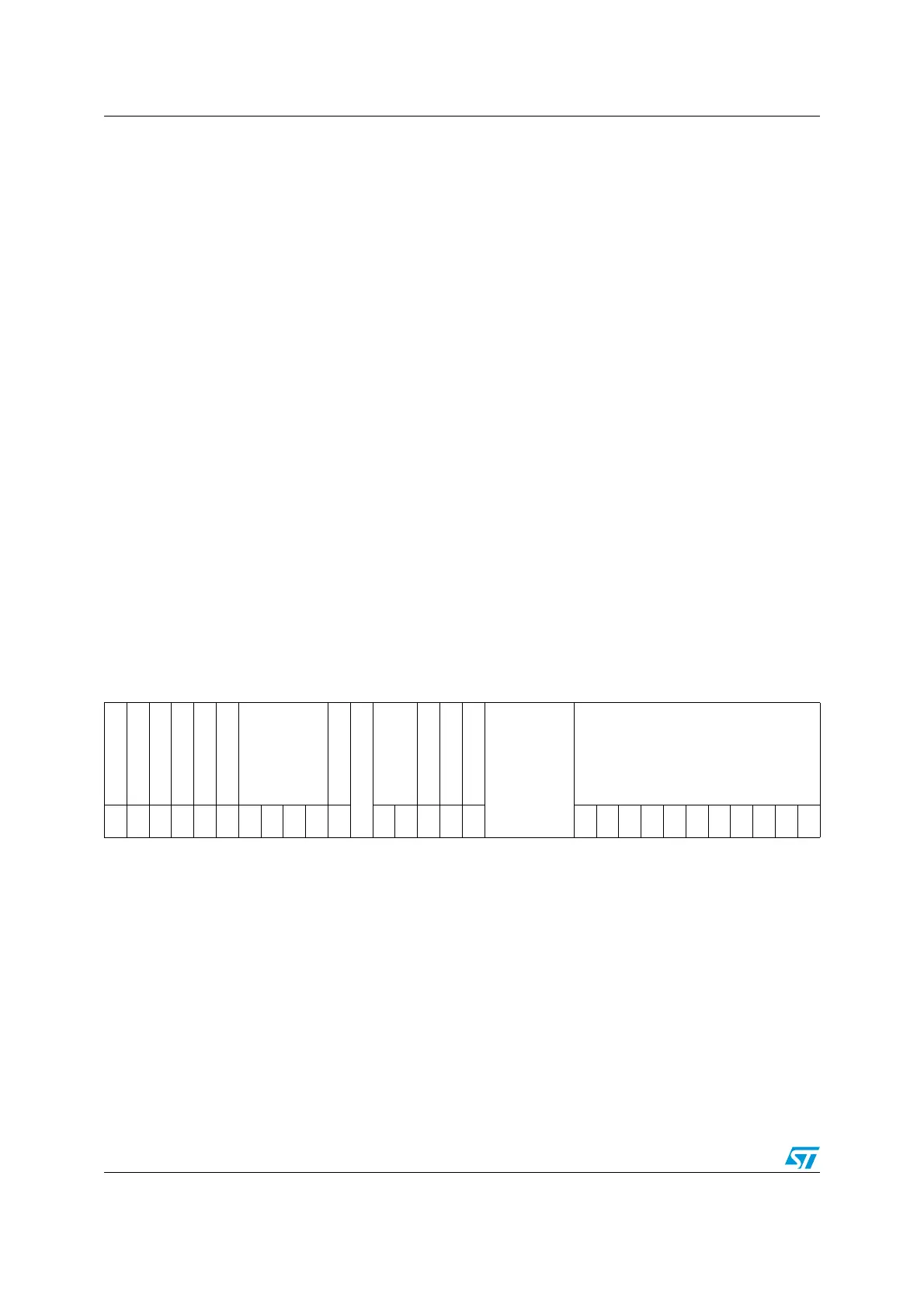

OTG device endpoint-x control register (OTG_HS_DIEPCTLx) (x = 0..7, where

x = Endpoint_number)

Address offset: 0x900 + (Endpoint_number × 0x20)

Reset value: 0x0000 0000

The application uses this register to control the behavior of each logical endpoint other than

endpoint 0.

Bit 9 BIM: BNA interrupt mask

0: Masked interrupt

1: Unmasked interrupt

Bit 8 OPEM: OUT packet error mask

0: Masked interrupt

1: Unmasked interrupt

Bits 7:3 Reserved, must be kept at reset value.

Bit 2 AHBERRM: AHB error mask

0: Masked interrupt

1: Unmasked interrupt

Bit 1 EPDM: Endpoint disabled interrupt mask

0: Masked interrupt

1: Unmasked interrupt

Bit 0 XFRCM: Transfer completed interrupt mask

0: Masked interrupt

1: Unmasked interrupt

313029282726252423222120191817161514131211109876543210

EPENA

EPDIS

SODDFRM

SD0PID/SEVNFRM

SNAK

CNAK

TXFNUM

Stall

Reserved

EPTYP

NAKSTS

EONUM/DPID

USBAEP

Reserved

MPSIZ

rsrswwwwrwrwrwrw

rw/

rs

rw rw r r rw rw rw rw rw rw rw rw rw rw rw rw

Bit 31 EPENA: Endpoint enable

The application sets this bit to start transmitting data on an endpoint.

The core clears this bit before setting any of the following interrupts on this endpoint:

– SETUP phase done

– Endpoint disabled

– Transfer completed

Bit 30 EPDIS: Endpoint disable

The application sets this bit to stop transmitting/receiving data on an endpoint, even before

the transfer for that endpoint is complete. The application must wait for the Endpoint

disabled interrupt before treating the endpoint as disabled. The core clears this bit before

setting the Endpoint disabled interrupt. The application must set this bit only if Endpoint

enable is already set for this endpoint.

Loading...

Loading...