RM0090 Flexible static memory controller (FSMC)

Doc ID 018909 Rev 4 1346/1422

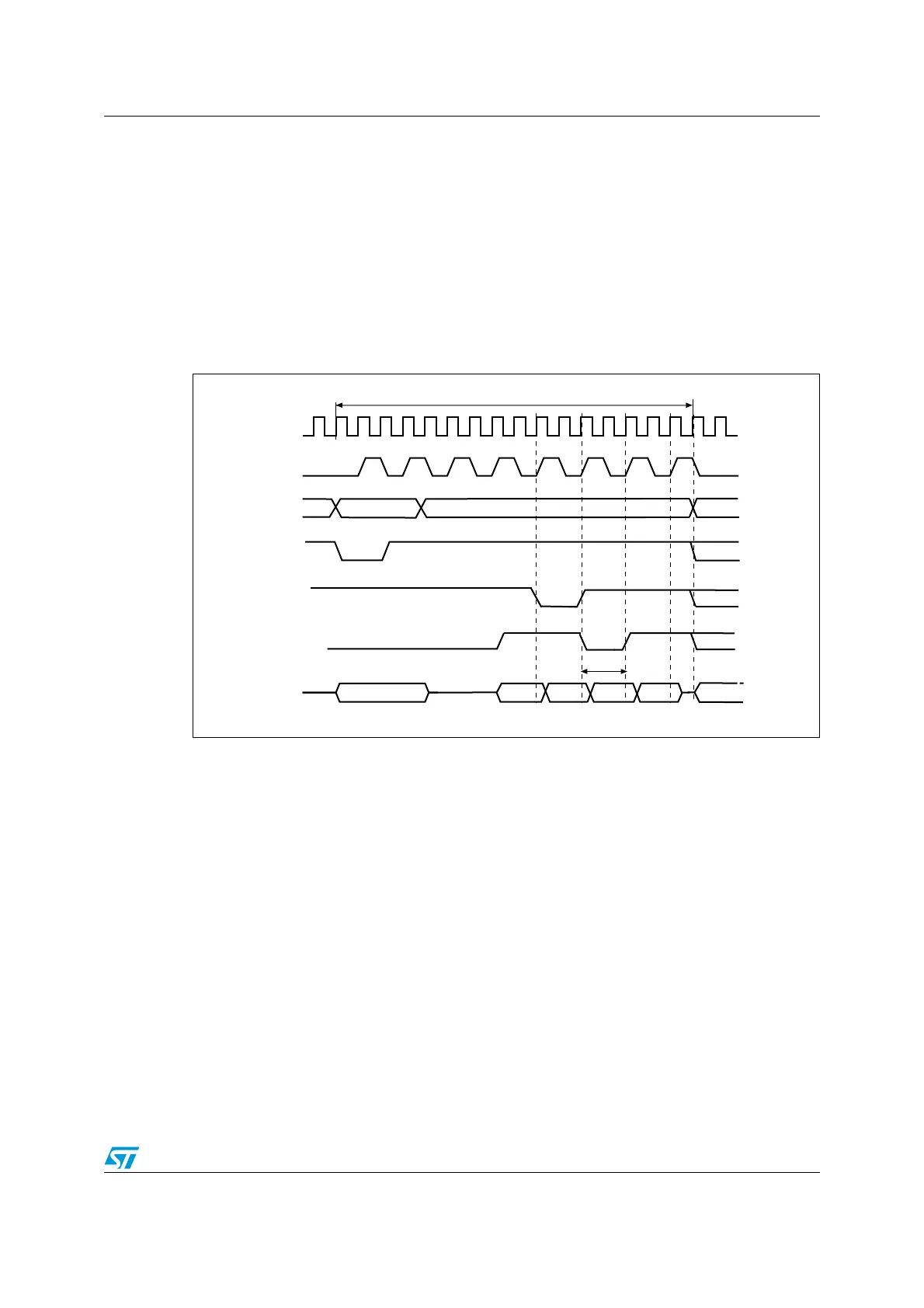

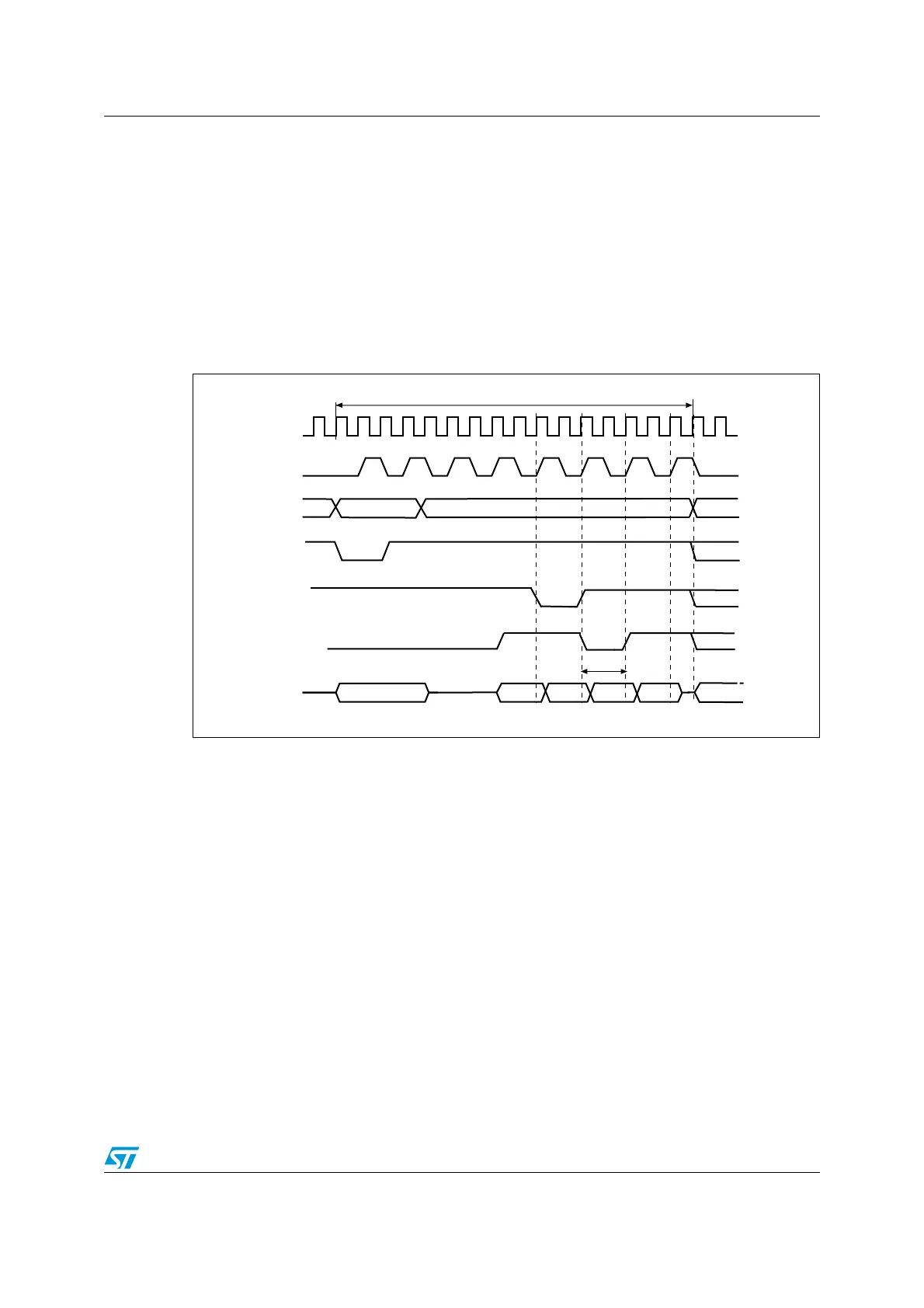

During wait-state insertion via the NWAIT signal, the controller continues to send clock

pulses to the memory, keeping the chip select and output enable signals valid, and does not

consider the data valid.

There are two timing configurations for the NOR Flash NWAIT signal in burst mode:

● Flash memory asserts the NWAIT signal one data cycle before the wait state (default

after reset)

● Flash memory asserts the NWAIT signal during the wait state

These two NOR Flash wait state configurations are supported by the FSMC, individually for

each chip select, thanks to the WAITCFG bit in the FSMC_BCRx registers (x = 0..3).

Figure 420. Wait configurations

aaddr[15:0] data data

addr[25:16]

Memory transaction = burst of 4 half words

HCLK

CLK

A[25:16]

NADV

NWAIT

(WAITCFG = 1)

A/D[15:0]

inserted wait state

data

NWAIT

(WAITCFG = 0)

ai15798b

Loading...

Loading...