Ethernet (ETH): media access control (MAC) with DMA controller RM0090

993/1422 Doc ID 018909 Rev 4

Ethernet MMC receive interrupt mask register (ETH_MMCRIMR)

Address offset: 0x010C

Reset value: 0x0000 0000

The Ethernet MMC receive interrupt mask register maintains the masks for interrupts

generated when the receive statistic counters reach half their maximum value. (MSB of the

counter is set.) It is a 32-bit wide register.

Bit 15 TGFMSCS: Transmitted good frames more single collision status

This bit is set when the transmitted, good frames after more than a single collision, counter

reaches half the maximum value.

Bit 14 TGFSCS: Transmitted good frames single collision status

This bit is set when the transmitted, good frames after a single collision, counter reaches half

the maximum value.

Bits 13:0 Reserved, must be kept at reset value.

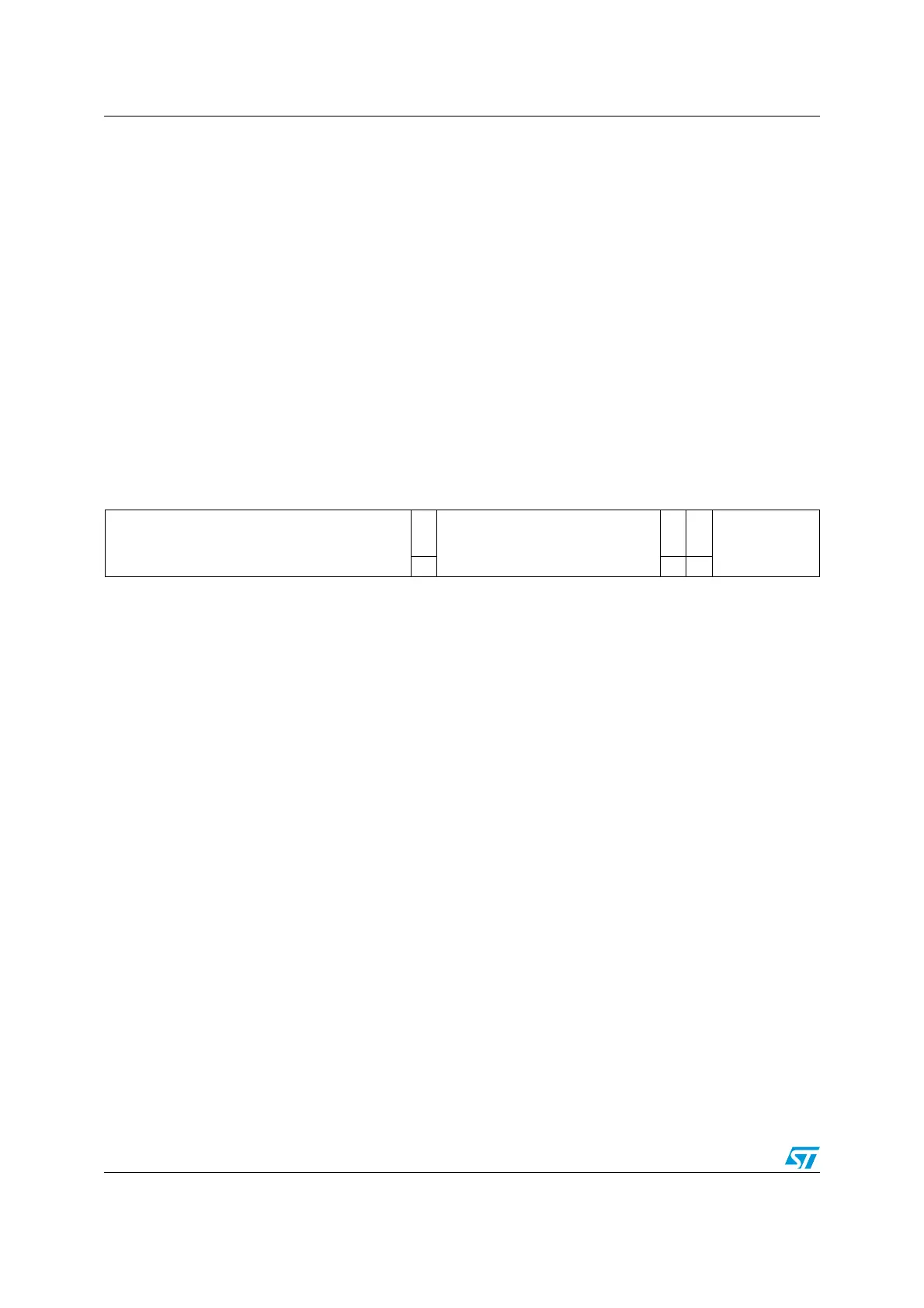

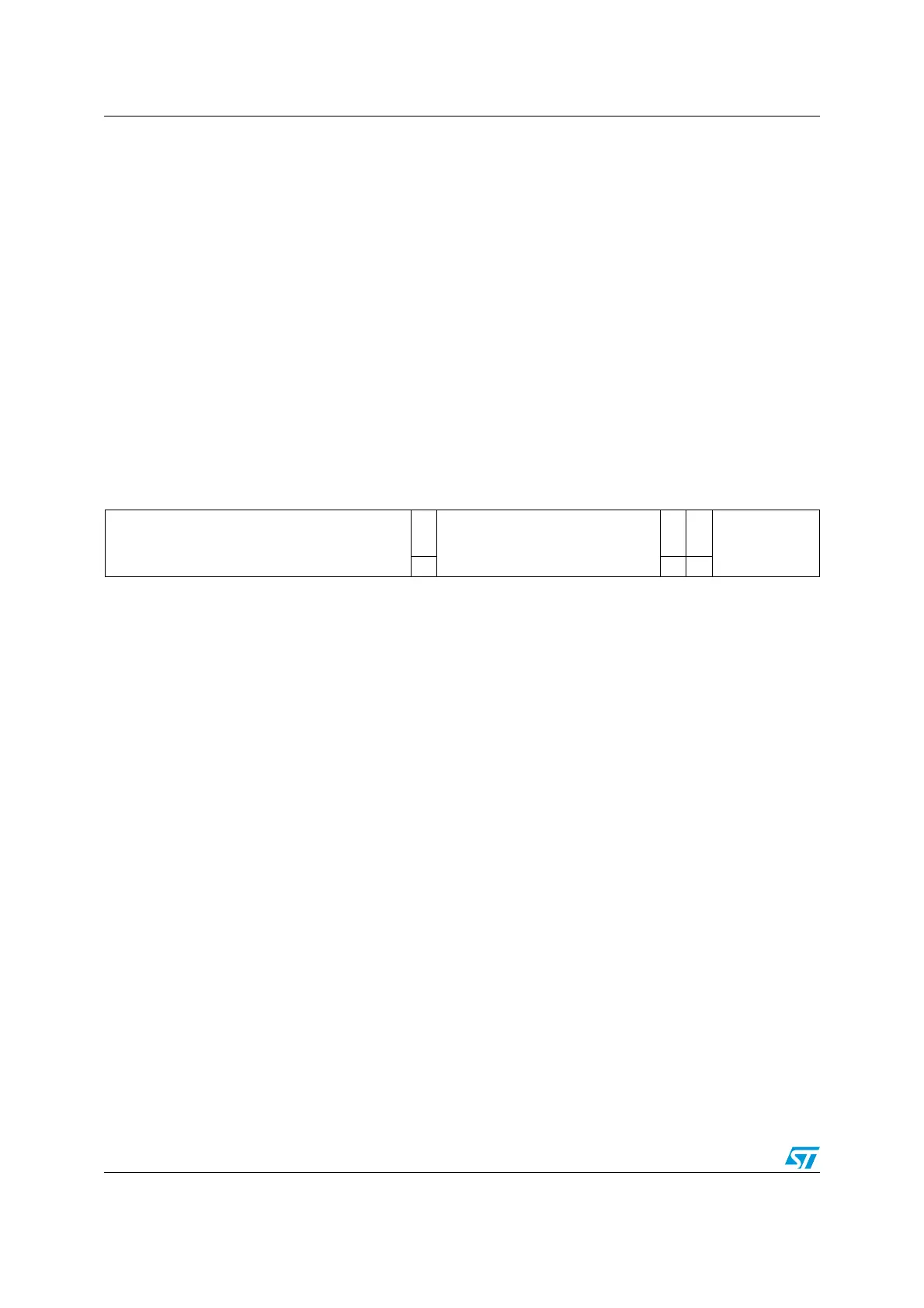

31302928272625242322212019181716151413121110987 6 5 43210

Reserved

RGUFM

Reserved

RFAEM

RFCEM

Reserved

rw rw rw

Bits 31:18 Reserved, must be kept at reset value.

Bit 17 RGUFM: Received good unicast frames mask

Setting this bit masks the interrupt when the received, good unicast frames, counter reaches

half the maximum value.

Bits 16:7 Reserved, must be kept at reset value.

Bit 6 RFAEM: Received frames alignment error mask

Setting this bit masks the interrupt when the received frames, with alignment error, counter

reaches half the maximum value.

Bit 5 RFCEM: Received frame CRC error mask

Setting this bit masks the interrupt when the received frames, with CRC error, counter

reaches half the maximum value.

Bits 4:0 Reserved, must be kept at reset value.

Loading...

Loading...