Ethernet (ETH): media access control (MAC) with DMA controller RM0090

999/1422 Doc ID 018909 Rev 4

the system time every clock cycle of HCLK. In Fine update mode, the value in this register is

added to the system time whenever the accumulator gets an overflow.

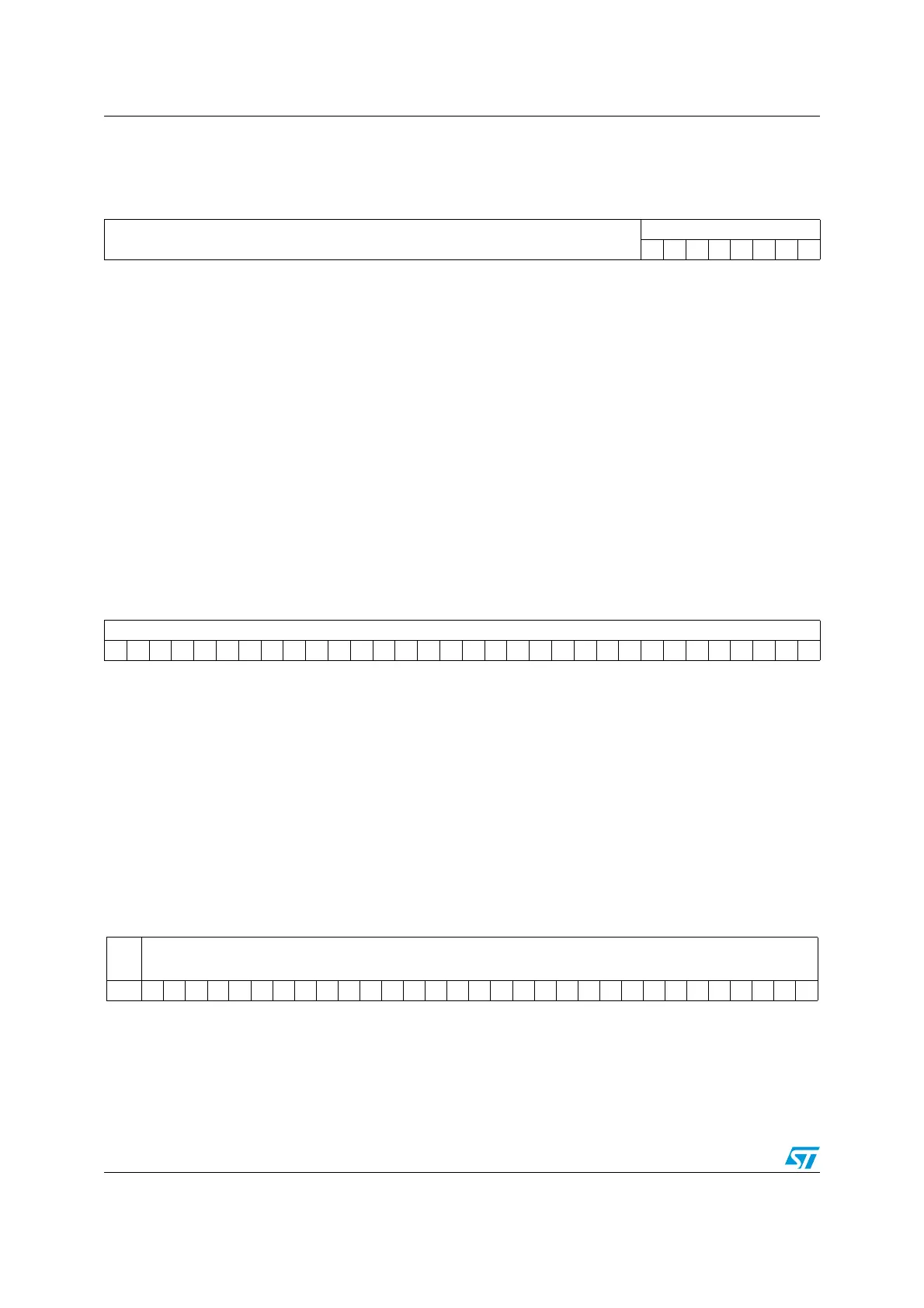

Ethernet PTP time stamp high register (ETH_PTPTSHR)

Address offset: 0x0708

Reset value: 0x0000 0000

This register contains the most significant (higher) 32 time bits. This read-only register

contains the seconds system time value. The Time stamp high register, along with Time

stamp low register, indicates the current value of the system time maintained by the MAC.

Though it is updated on a continuous basis.

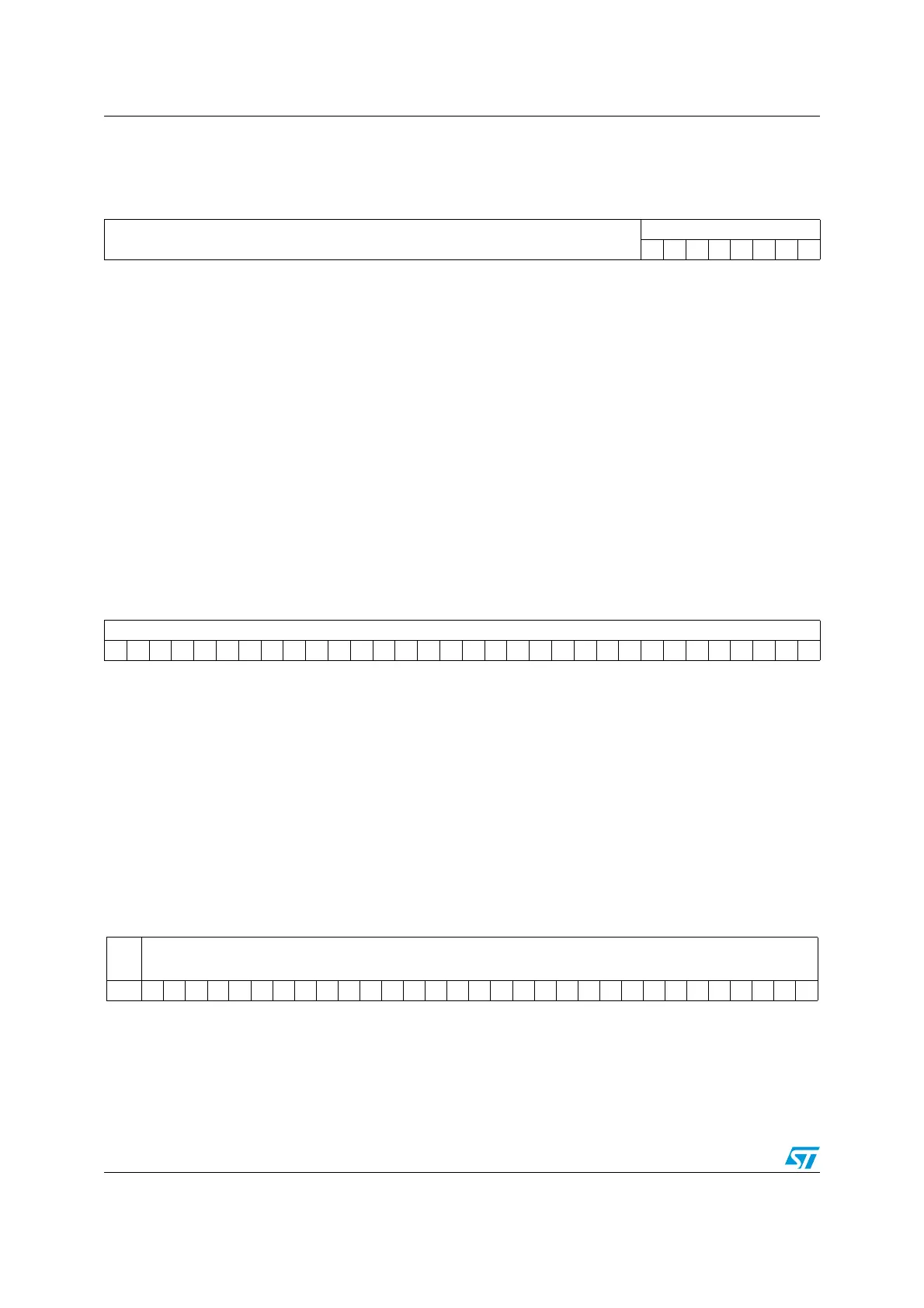

Ethernet PTP time stamp low register (ETH_PTPTSLR)

Address offset: 0x070C

Reset value: 0x0000 0000

This register contains the least significant (lower) 32 time bits. This read-only register

contains the subsecond system time value.

313029282726252423222120191817161514131211109876543210

Reserved

STSSI

rw rw rw rw rw rw rw rw

Bits 31:8 Reserved, must be kept at reset value.

Bits 7:0 STSSI: System time subsecond increment

The value programmed in this register is added to the contents of the subsecond value of the

system time in every update.

For example, to achieve 20 ns accuracy, the value is: 20 / 0.467 = ~ 43 (or 0x2A).

313029282726252423222120191817161514131211109876543210

STS

rrrrrrrrrrrrrrrrrrrrrrrrrrrrrrrr

Bits 31:0 STS: System time second

The value in this field indicates the current value in seconds of the System Time maintained

by the core.

313029282726252423222120191817161514131211109876543210

STPNS

STSS

r rrrrrrrrrrrrrrrrrrrrrrrrrrrrrrr

Loading...

Loading...