MPC5604B/C Microcontroller Reference Manual, Rev. 8

108 Freescale Semiconductor

6.7.6.2 Progressive clock switching

Progressive clock switching allows to switch the system clock to FMPLL output clock stepping through

different division factors. This means that the current consumption gradually increases and, in turn, voltage

regulator response is improved.

This feature can be enabled by programming CR[EN_PLL_SW] bit. When enabled, the system clock is

switched to divided PHI. The FMPLL_clk divider is then progressively decreased to the target divider as

shown in Table 6-15.

Figure 6-9. FMPLL output clock division flow during progressive switching

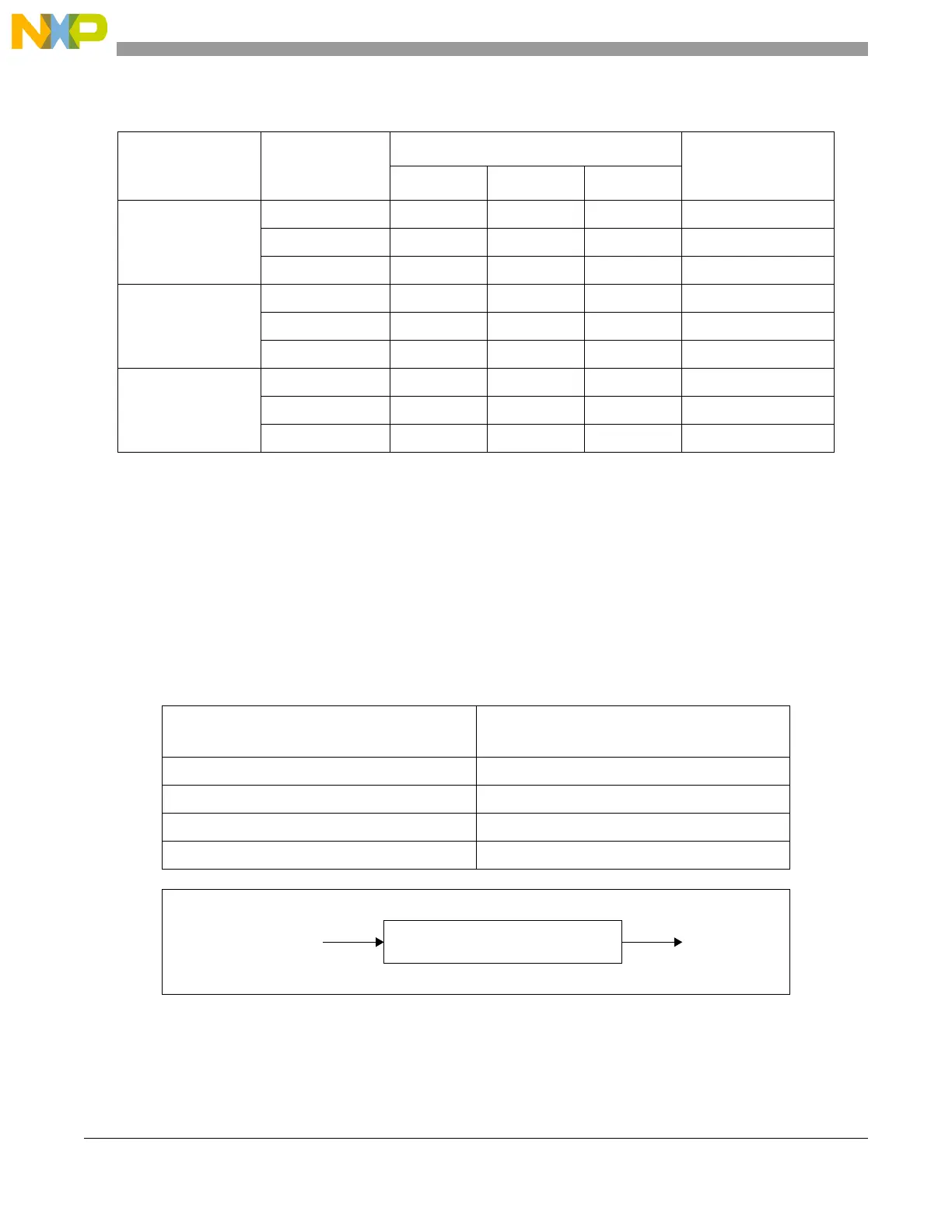

Table 6-14. FMPLL lookup table

Crystal frequency

(MHz)

FMPLL output

frequency (MHz)

CR field values

VCO frequency (MHz)

IDF ODF NDIV

8320232256

64 0 2 64 512

80 0 1 40 320

16 32 1 2 32 256

64 1 2 64 512

80 1 1 40 320

40 32 4 2 32 256

64 4 2 64 512

80 3 1 32 320

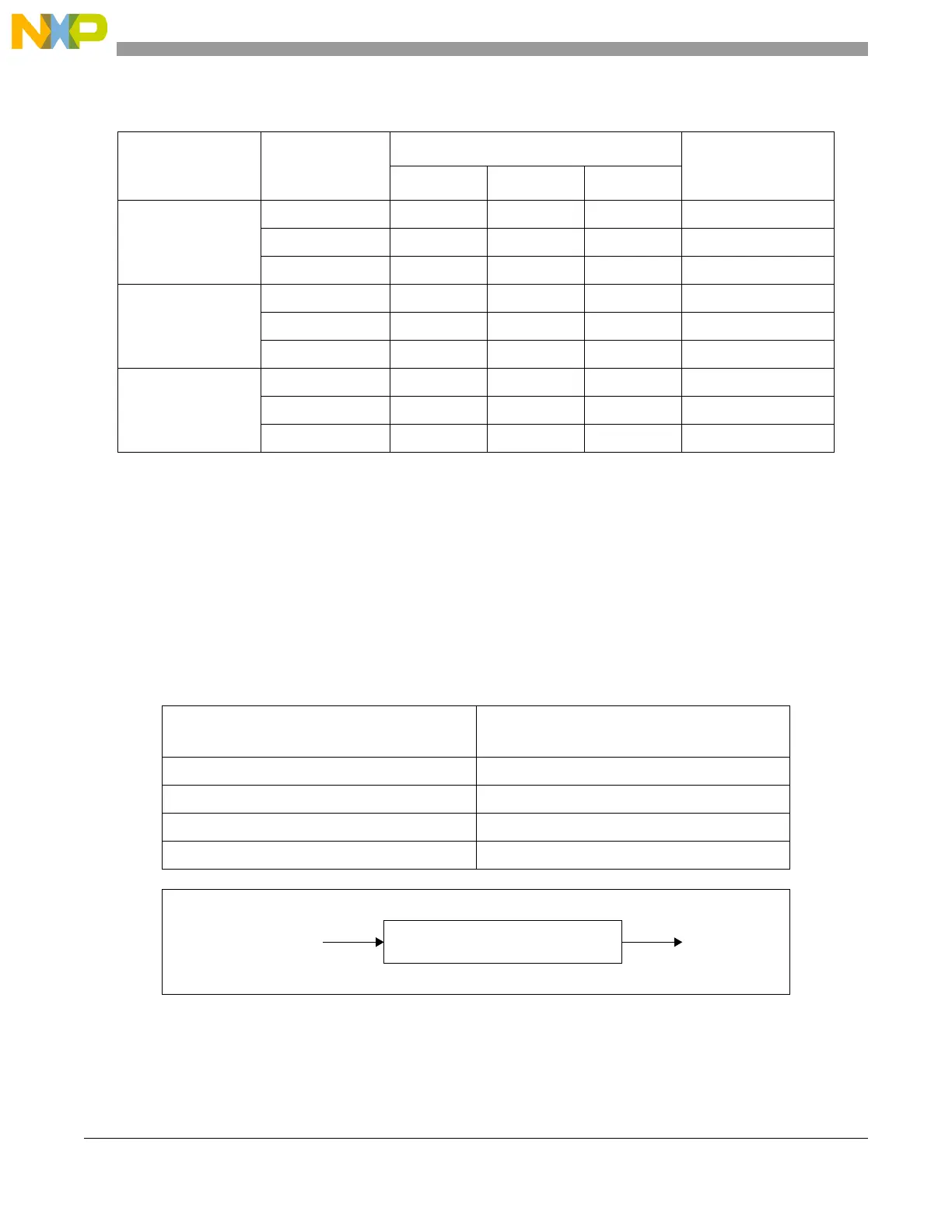

Table 6-15. Progressive clock switching on pll_select rising edge

Number of FMPLL output clock cycles

FMPLL_clk frequency

(FMPLL output clock frequency)

8 (FMPLL output clock frequency)/8

16 (FMPLL output clock frequency)/4

32 (FMPLL output clock frequency)/2

onward FMPLL output clock frequency

FMPLL output clock FMPLL_clkDivision factors of 8, 4, 2 or 1

Loading...

Loading...