MPC5604B/C Microcontroller Reference Manual, Rev. 8

196 Freescale Semiconductor

This register provides dedicated bits to disable functional reset sources.When a functional reset source is

disabled, the associated functional event will trigger either a SAFE mode request or an interrupt request

(see Section 9.3.1.5, “Functional Event Alternate Request Register (RGM_FEAR)). It can be accessed in

read/write in either supervisor mode or test mode. It can be accessed in read only in user mode. Each byte

can be written only once after power-on reset.

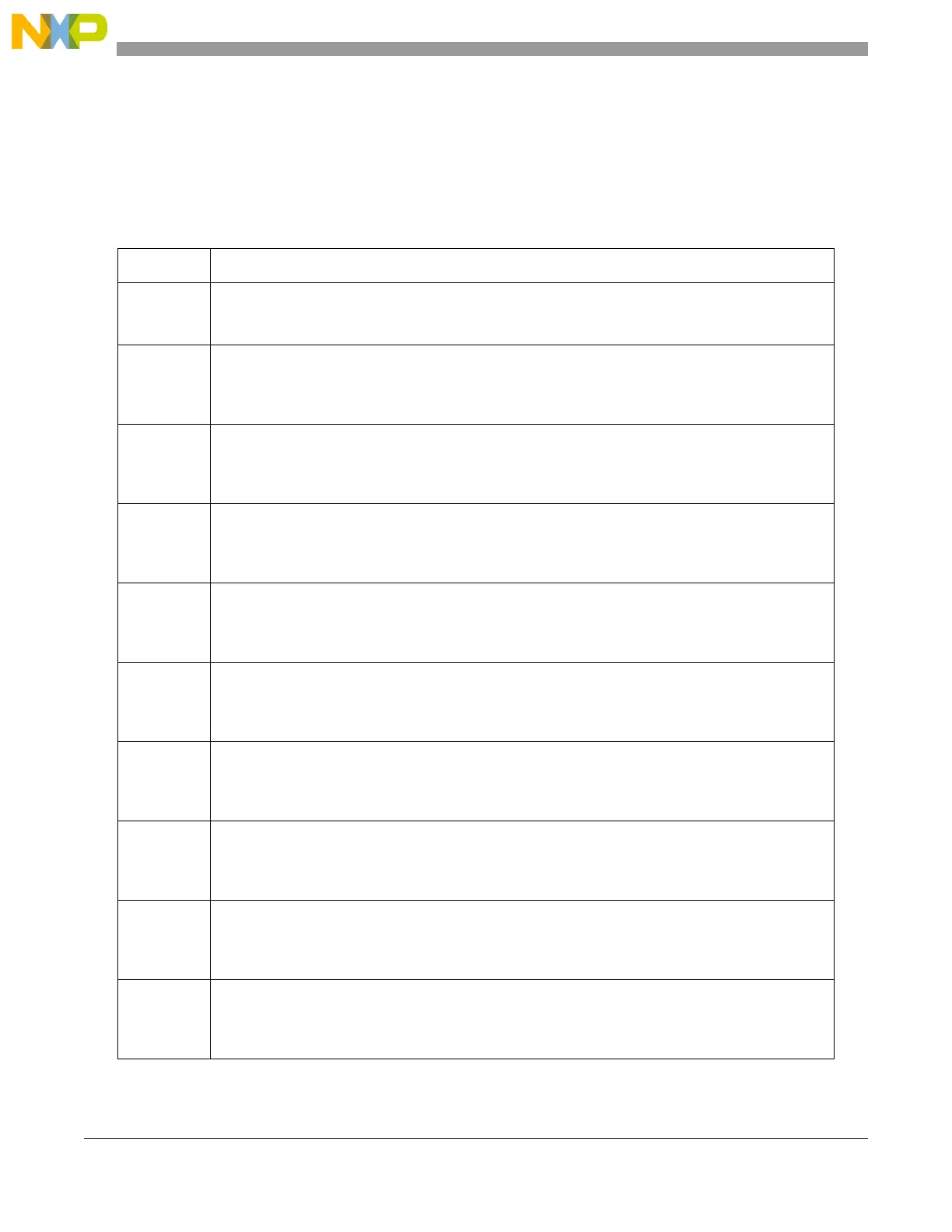

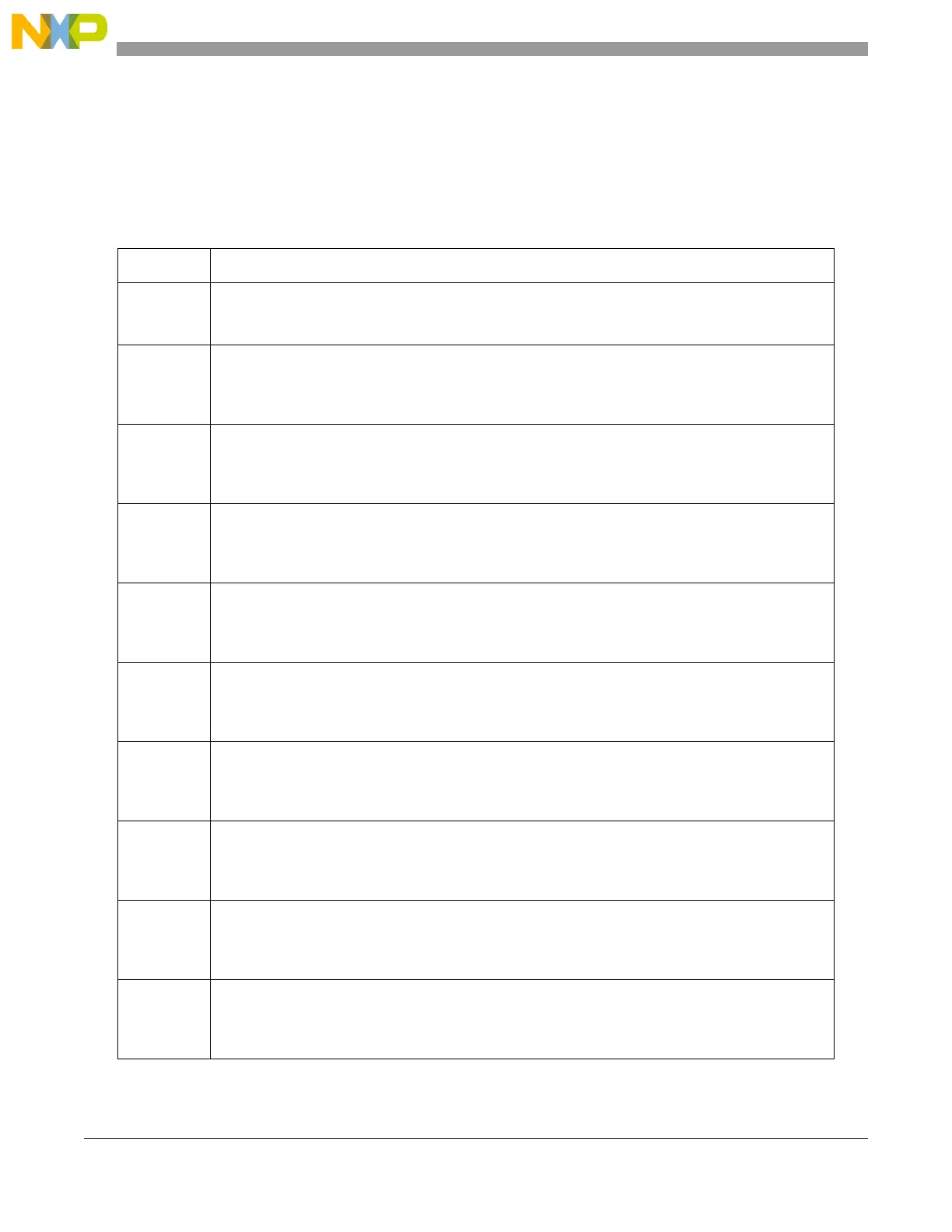

Table 9-5. Functional Event Reset Disable Register (RGM_FERD) Field Descriptions

Field Description

D_EXR Disable External Reset

0 An external reset event triggers a reset sequence

1 An external reset event generates a SAFE mode request

D_FLASH Disable code or data flash fatal error

0 A code or data flash fatal error event triggers a reset sequence

1 A code or data flash fatal error event generates either a SAFE mode or an interrupt request

depending on the value of RGM_FEAR.AR_FLASH

D_LVD45 Disable 4.5 V low-voltage detected

0 A 4.5 V low-voltage detected event triggers a reset sequence

1 A 4.5 V low-voltage detected event generates either a SAFE mode or an interrupt request

depending on the value of RGM_FEAR.AR_LVD45

D_CMU_FH

L

Disable CMU clock frequency higher/lower than reference

0 A CMU clock frequency higher/lower than reference event triggers a reset sequence

1 A CMU clock frequency higher/lower than reference event generates either a SAFE mode or an

interrupt request depending on the value of RGM_FEAR.AR_CMU_FHL

D_CMU_OL

R

Disable FXOSC frequency lower than reference

0 A FXOSC frequency lower than reference event triggers a reset sequence

1 A FXOSC frequency lower than reference event generates either a SAFE mode or an interrupt

request depending on the value of RGM_FEAR.AR_CMU_OLR

D_FMPLL Disable FMPLL fail

0 A FMPLL fail event triggers a reset sequence

1 A FMPLL fail event generates either a SAFE mode or an interrupt request depending on the value

of RGM_FEAR.AR_FMPLL

D_CHKSTO

P

Disable checkstop reset

0 A checkstop reset event triggers a reset sequence

1 A checkstop reset event generates either a SAFE mode or an interrupt request depending on the

value of RGM_FEAR.AR_CHKSTOP

D_SOFT Disable software reset

0 A software reset event triggers a reset sequence

1 A software reset event generates either a SAFE mode or an interrupt request depending on the

value of RGM_FEAR.AR_SOFT

D_CORE Disable debug control core reset

0 A debug control core reset event triggers a reset sequence

1 A debug control core reset event generates either a SAFE mode or an interrupt request depending

on the value of RGM_FEAR.AR_CORE

D_JTAG Disable JTAG initiated reset

0 A JTAG initiated reset event triggers a reset sequence

1 A JTAG initiated reset event generates either a SAFE mode or an interrupt request depending on

the value of RGM_FEAR.AR_JTAG

Loading...

Loading...