MPC5604B/C Microcontroller Reference Manual, Rev. 8

Freescale Semiconductor 197

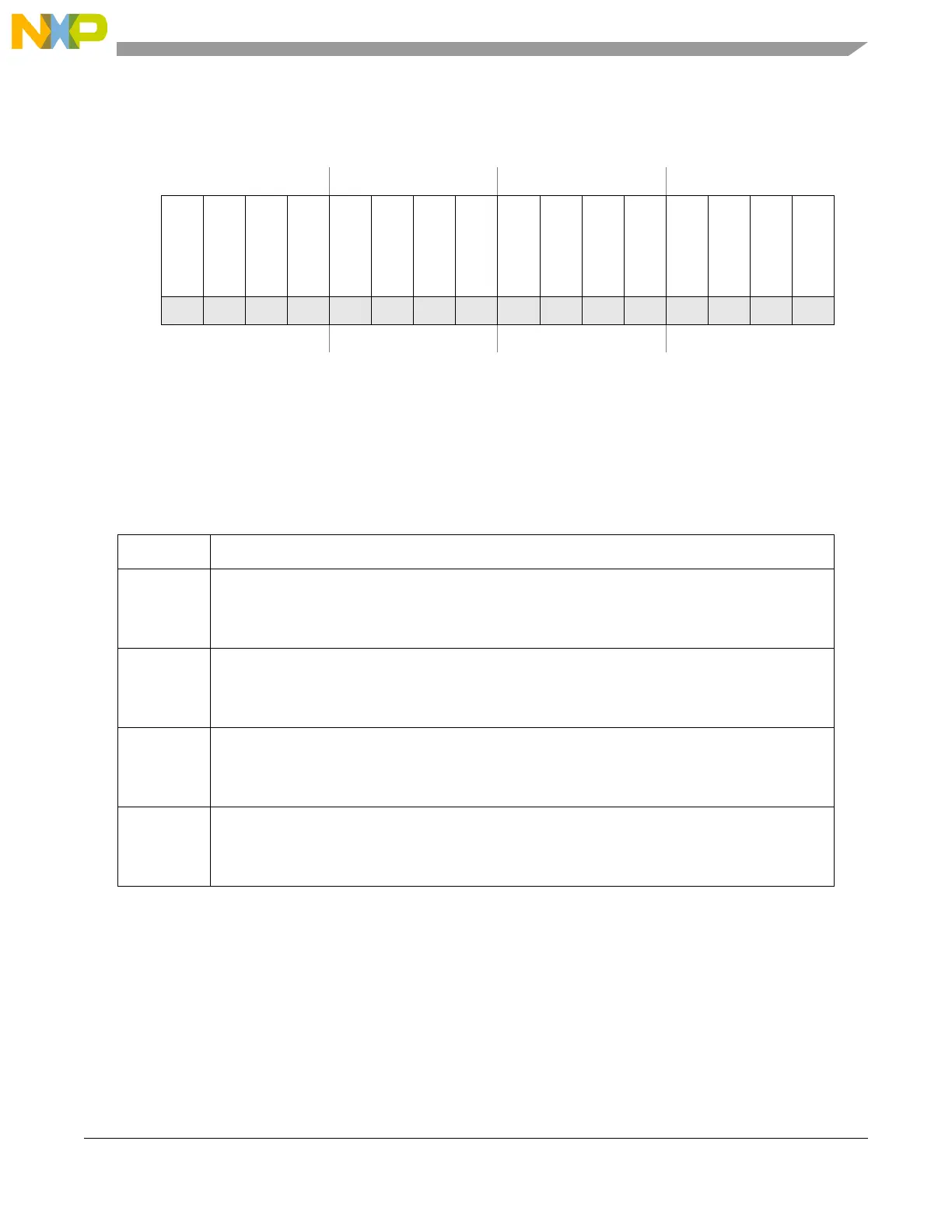

9.3.1.4 Destructive Event Reset Disable Register (RGM_DERD)

This register provides dedicated bits to disable particular destructive reset sources. When a destructive

reset source is disabled, the associated destructive event will trigger either a safe mode request or an

interrupt request (see Section 9.3.1.6, “Destructive Event Alternate Request Register (RGM_DEAR)).

Address 0xC3FE_4006 Access: Read

0123456789101112131415

R

000000000000

D_LVD27

D_SWT

D_LVD12_PD1

D_LVD12_PD0

W

POR0000000000000000

Figure 9-5. Destructive Event Reset Disable Register (RGM_DERD)

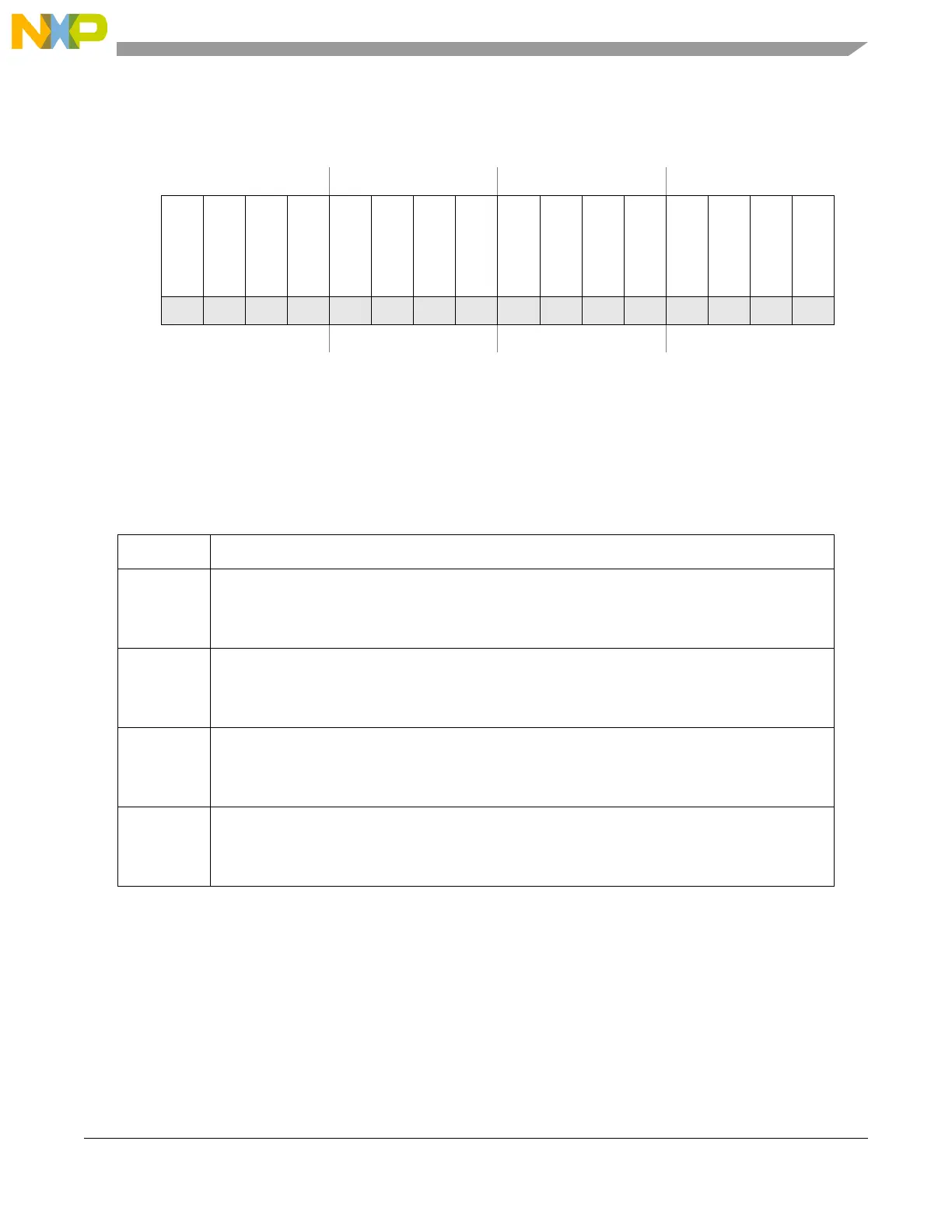

Table 9-6. Destructive Event Reset Disable Register (RGM_DERD) Field Descriptions

Field Description

D_LVD27 Disable 2.7 V low-voltage detected

0 A 2.7 V low-voltage detected event triggers a reset sequence

1 A 2.7 V low-voltage detected event generates either a SAFE mode or an interrupt request

depending on the value of RGM_DEAR.AR_LVD27

D_SWT Disable software watchdog timer

0 A software watchdog timer event triggers a reset sequence

1 A software watchdog timer event generates either a SAFE mode or an interrupt request depending

on the value of RGM_DEAR.

D_LVD12_P

D1

Disable 1.2 V low-voltage detected (power domain #1)

0 A 1.2 V low-voltage detected (power domain #1) event triggers a reset sequence

1 A 1.2 V low-voltage detected (power domain #1) event generates either a SAFE mode or an

interrupt request depending on the value of RGM_DEAR.AR_LVD12_PD1

D_LVD12_P

D0

Disable 1.2 V low-voltage detected (power domain #0)

0 A 1.2 V low-voltage detected (power domain #0) event triggers a reset sequence

1 A 1.2 V low-voltage detected (power domain #0) event generates either a SAFE mode or an

interrupt request depending on the value of RGM_DEAR.AR_LVD12_PD0

Loading...

Loading...