MPC5604B/C Microcontroller Reference Manual, Rev. 8

Freescale Semiconductor 201

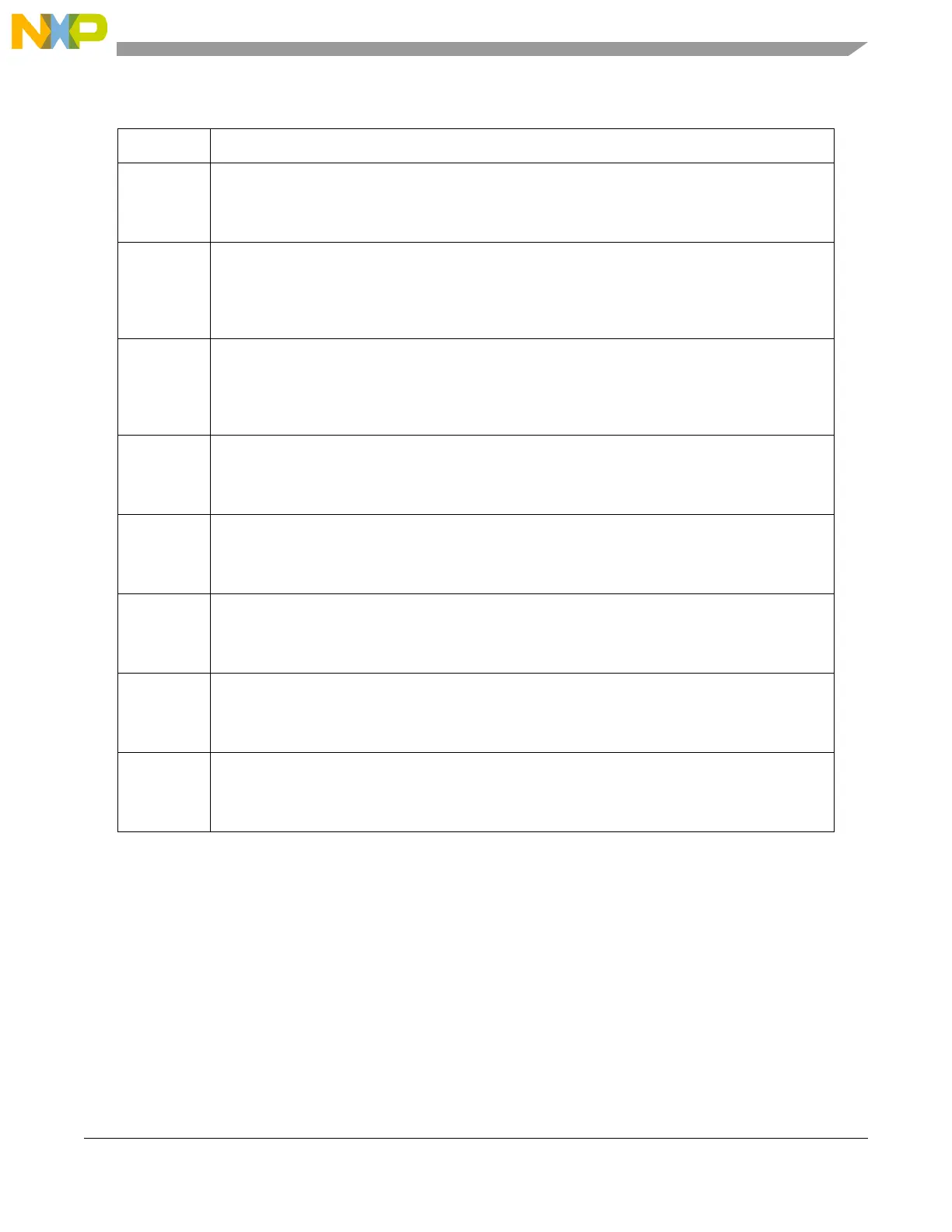

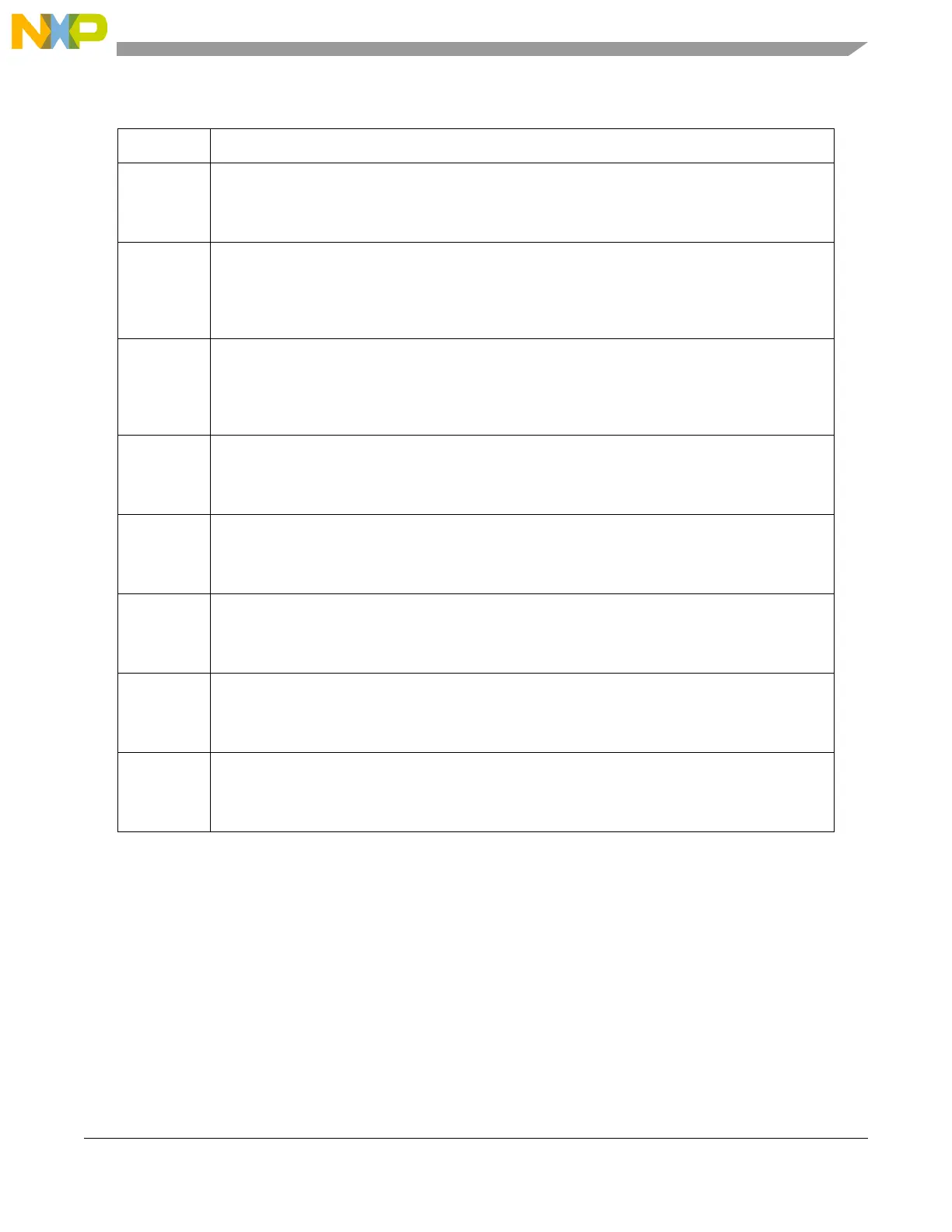

SS_LVD45 Short Sequence for 4.5 V low-voltage detected

0 The reset sequence triggered by a 4.5 V low-voltage detected event will start from PHASE1

1 The reset sequence triggered by a 4.5 V low-voltage detected event will start from PHASE3,

skipping PHASE1 and PHASE2

SS_CMU_F

HL

Short Sequence for CMU clock frequency higher/lower than reference

0 The reset sequence triggered by a CMU clock frequency higher/lower than reference event will

start from PHASE1

1 The reset sequence triggered by a CMU clock frequency higher/lower than reference event will

start from PHASE3, skipping PHASE1 and PHASE2

SS_CMU_O

LR

Short Sequence for FXOSC frequency lower than reference

0 The reset sequence triggered by a FXOSC frequency lower than reference event will start from

PHASE1

1 The reset sequence triggered by a FXOSC frequency lower than reference event will start from

PHASE3, skipping PHASE1 and PHASE2

SS_FMPLL Short Sequence for FMPLL fail

0 The reset sequence triggered by a FMPLL fail event will start from PHASE1

1 The reset sequence triggered by a FMPLL fail event will start from PHASE3, skipping PHASE1

and PHASE2

SS_CHKST

OP

Short Sequence for checkstop reset

0 The reset sequence triggered by a checkstop reset event will start from PHASE1

1 The reset sequence triggered by a checkstop reset event will start from PHASE3, skipping

PHASE1 and PHASE2

SS_SOFT Short Sequence for software reset

0 The reset sequence triggered by a software reset event will start from PHASE1

1 The reset sequence triggered by a software reset event will start from PHASE3, skipping PHASE1

and PHASE2

SS_CORE Short Sequence for debug control core reset

0 The reset sequence triggered by a debug control core reset event will start from PHASE1

1 The reset sequence triggered by a debug control core reset event will start from PHASE3, skipping

PHASE1 and PHASE2

SS_JTAG Short Sequence for JTAG initiated reset

0 The reset sequence triggered by a JTAG initiated reset event will start from PHASE1

1 The reset sequence triggered by a JTAG initiated reset event will start from PHASE3, skipping

PHASE1 and PHASE2

Table 9-9. Functional Event Short Sequence Register (RGM_FESS) Field Descriptions (continued)

Field Description

Loading...

Loading...