MPC5604B/C Microcontroller Reference Manual, Rev. 8

Freescale Semiconductor 311

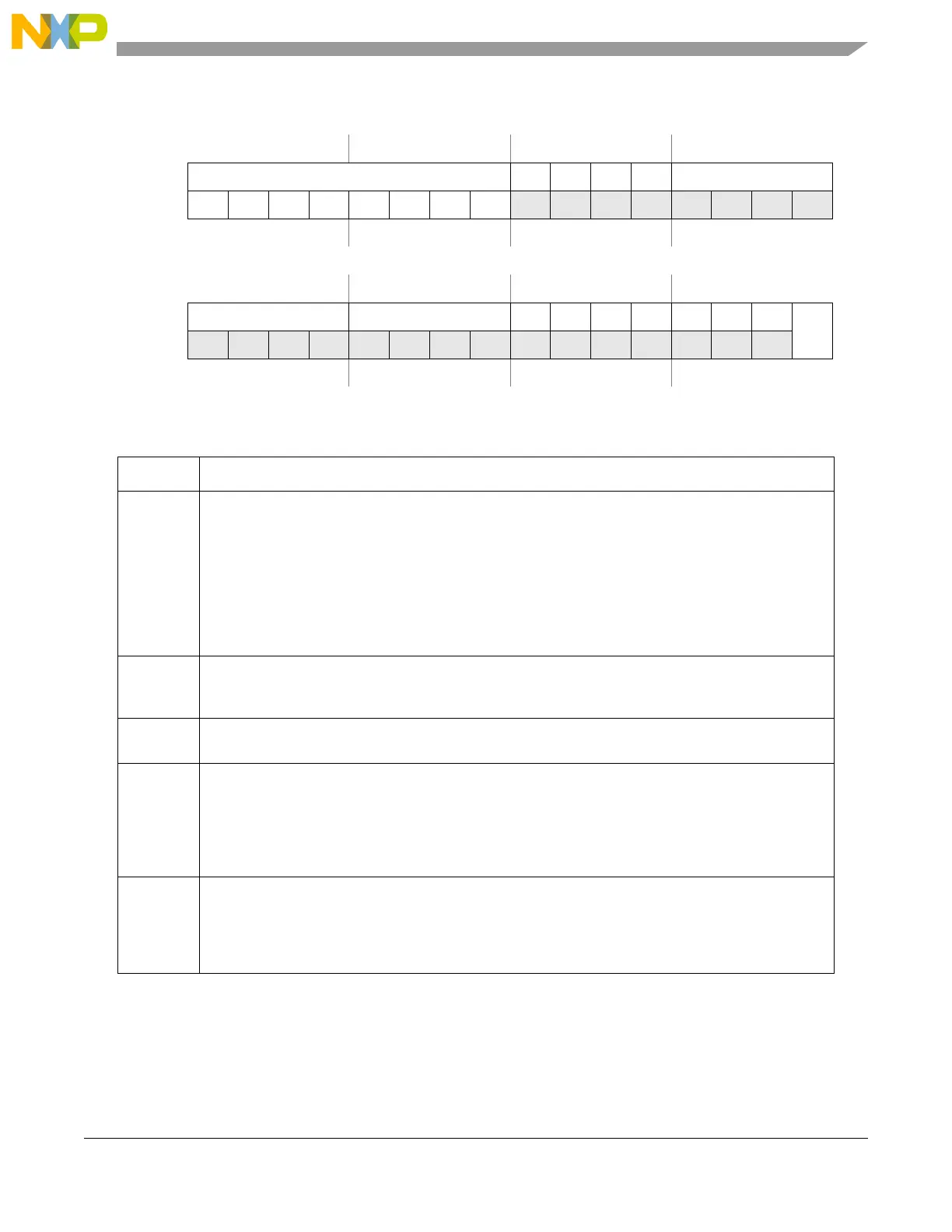

18.5.2.2 MPU Error Address Register, Slave Port n (MPU_EARn)

When the MPU detects an access error on slave port n, the 32-bit reference address is captured in this

read-only register and the corresponding bit in the MPU_CESR[SPERR] field set. Additional information

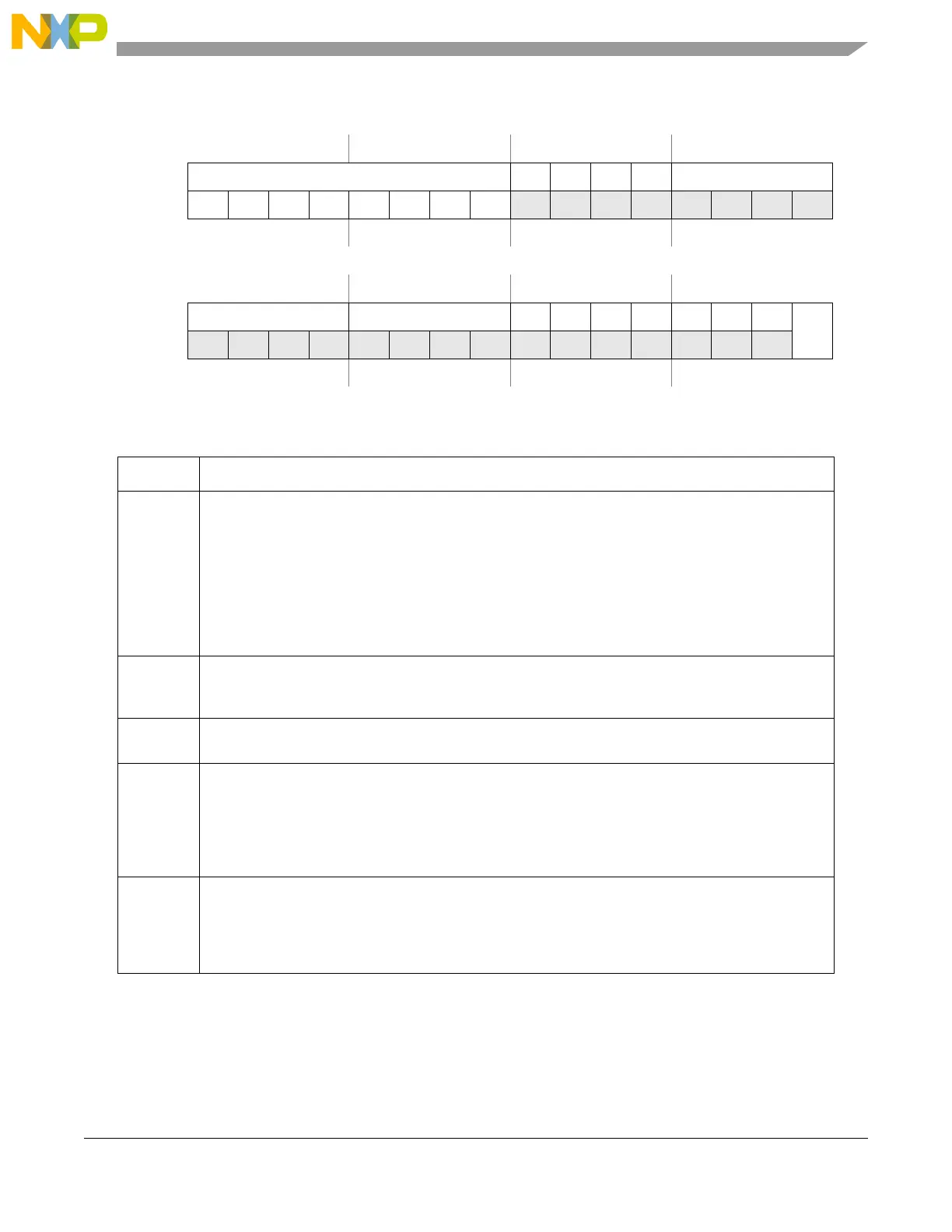

Offset: 0x000 Access: Read/Partial Write

0123456789101112131415

R SPERR[7:0] 1 0 0 0 HRL

W w1c w1c w1c w1c w1c w1c w1c w1c

Reset000000001000* * * *

16 17 18 19 20 21 22 23 24 25 26 27 28 29 30 31

RNSP NRGD 00000 0 0

VLD

W

Reset********00000000

Figure 18-2. MPU Control/Error Status Register (MPU_CESR)

Table 18-2. MPU_CESR field descriptions

Field Description

SPERRn Slave Port n Error, where the slave port number matches the bit number.

Each bit in this field represents a flag maintained by the MPU for signaling the presence of a captured

error contained in the MPU_EARn and MPU_EDRn registers. The individual bit is set when the

hardware detects an error and records the faulting address and attributes. It is cleared when the

corresponding bit is written as a logical one. If another error is captured at the exact same cycle as a

write of a logical one, this flag remains set. A “find first one” instruction (or equivalent) can be used to

detect the presence of a captured error.

0 The corresponding MPU_EARn/MPU_EDRn registers do not contain a captured error.

1 The corresponding MPU_EARn/MPU_EDRn registers do contain a captured error.

HRL Hardware Revision Level

This field specifies the MPU’s hardware and definition revision level. It can be read by software to

determine the functional definition of the module.

NSP Number of Slave Ports

This field specifies the number of slave ports [1–8] connected to the MPU.

NRGD Number of Region Descriptors

This field specifies the number of region descriptors implemented in the MPU. The defined encodings

include:

0b0000 8 region descriptors

0b0001 12 region descriptors

0b0010 16 region descriptors

VLD Valid

This bit provides a global enable/disable for the MPU.

0 The MPU is disabled.

1 The MPU is enabled.

While the MPU is disabled, all accesses from all bus masters are allowed.

Loading...

Loading...