MPC5604B/C Microcontroller Reference Manual, Rev. 8

312 Freescale Semiconductor

about the faulting access is captured in the corresponding MPU_EDRn register at the same time. Note this

register and the corresponding MPU_EDRn register contain the most recent access error; there are no

hardware interlocks with the MPU_CESR[SPERR] field as the error registers are always loaded upon the

occurrence of each protection violation.

18.5.2.3 MPU Error Detail Register, Slave Port n (MPU_EDRn)

When the MPU detects an access error on slave port n, 32 bits of error detail are captured in this read-only

register and the corresponding bit in the MPU_CESR[SPERR] field set. Information on the faulting

address is captured in the corresponding MPU_EARn register at the same time. Note that this register and

the corresponding MPU_EARn register contain the most recent access error; there are no hardware

interlocks with the MPU_CESR[SPERR] field as the error registers are always loaded upon the occurrence

of each protection violation.

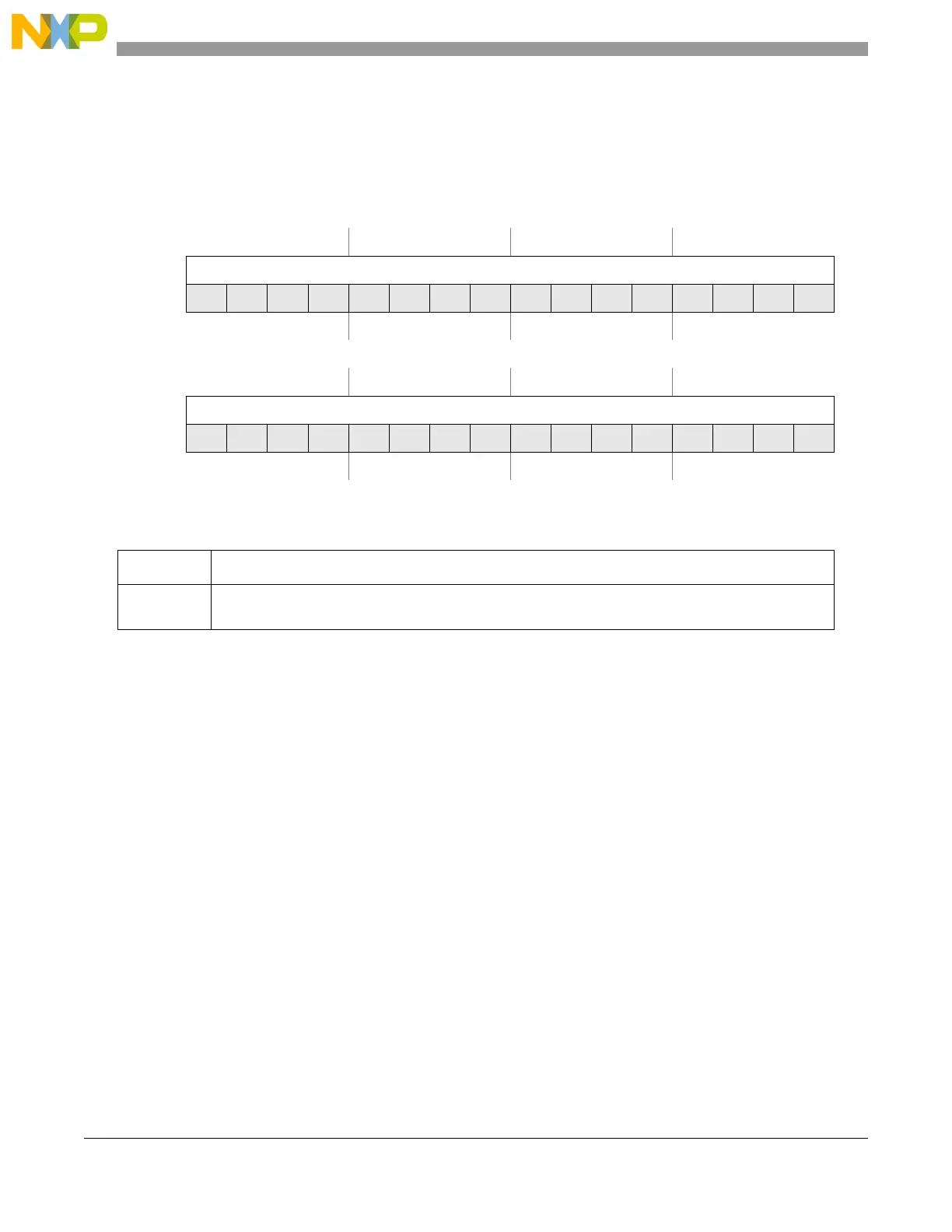

Offsets: 0x010–0x020 (3 registers) Access: Read

0123456789101112131415

R EADDR [31:16]

W

Reset––––––––––––––––

16 17 18 19 20 21 22 23 24 25 26 27 28 29 30 31

R EADDR [15:0]

W

Reset––––––––––––––––

Figure 18-3. MPU Error Address Register, Slave Port n (MPU_EARn)

Table 18-3. MPU_EARn field descriptions

Field Description

EADDR Error Address

This field is the reference address from slave port n that generated the access error.

Loading...

Loading...