MPC5604B/C Microcontroller Reference Manual, Rev. 8

360 Freescale Semiconductor

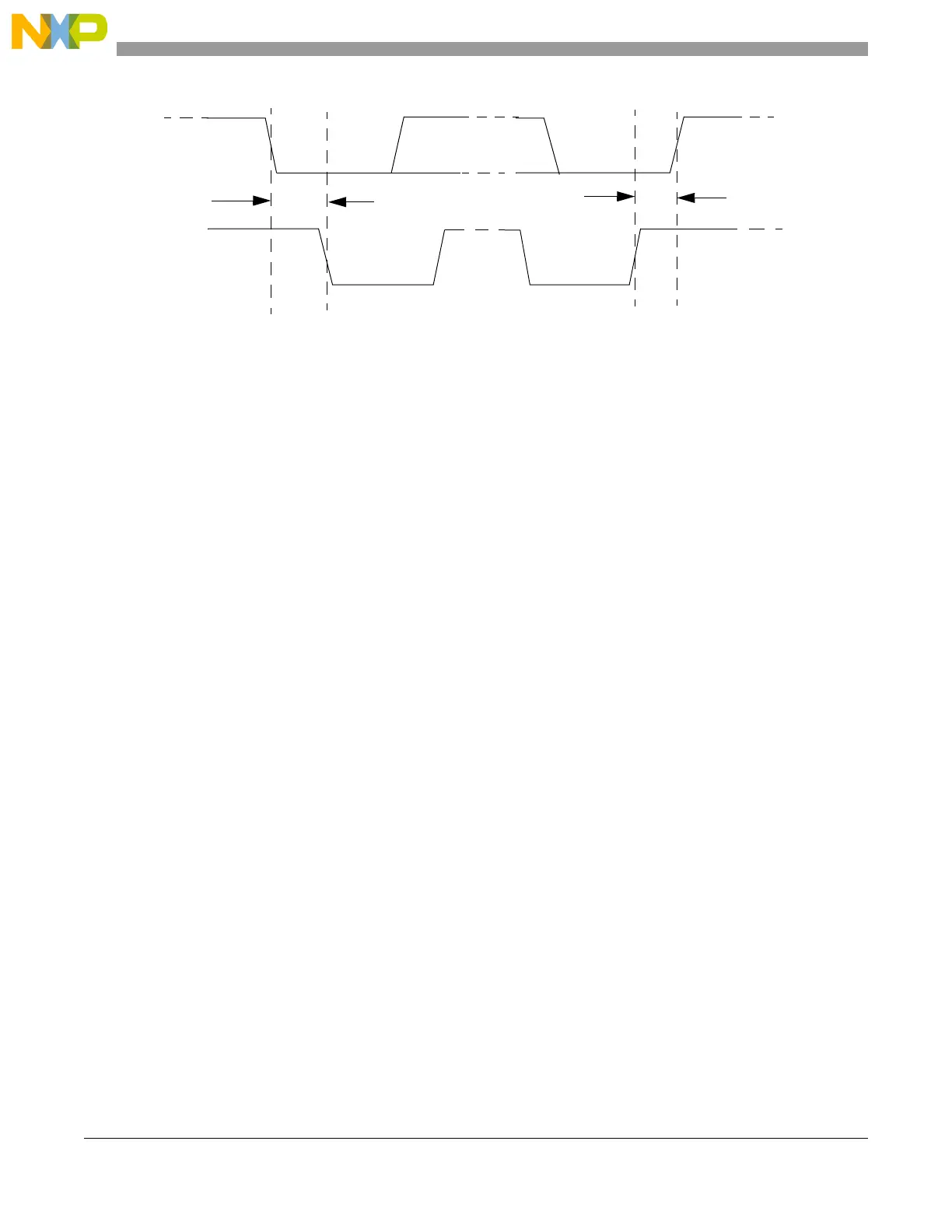

Figure 20-5. SCL divider and SDA hold

The equation used to generate the divider values from the IBFD bits is:

SCL Divider = MUL x {2 x (scl2tap + [(SCL_Tap -1) x tap2tap] + 2)} Eqn. 20-1

The SDA hold delay is equal to the CPU clock period multiplied by the SDA Hold value shown in

Table 20-7. The equation used to generate the SDA Hold value from the IBFD bits is:

SDA Hold = MUL x {scl2tap + [(SDA_Tap - 1) x tap2tap] + 3} Eqn. 20-2

The equation for SCL Hold values to generate the start and stop conditions from the IBFD bits is:

SCL Hold(start) = MUL x [scl2start + (SCL_Tap - 1) x tap2tap] Eqn. 20-3

SCL Hold(stop) = MUL x [scl2stop + (SCL_Tap - 1) x tap2tap] Eqn. 20-4

SDA

SCL

START condition STOP condition

SCL Hold(start)

SCL Hold(stop)

Loading...

Loading...