MPC5604B/C Microcontroller Reference Manual, Rev. 8

364 Freescale Semiconductor

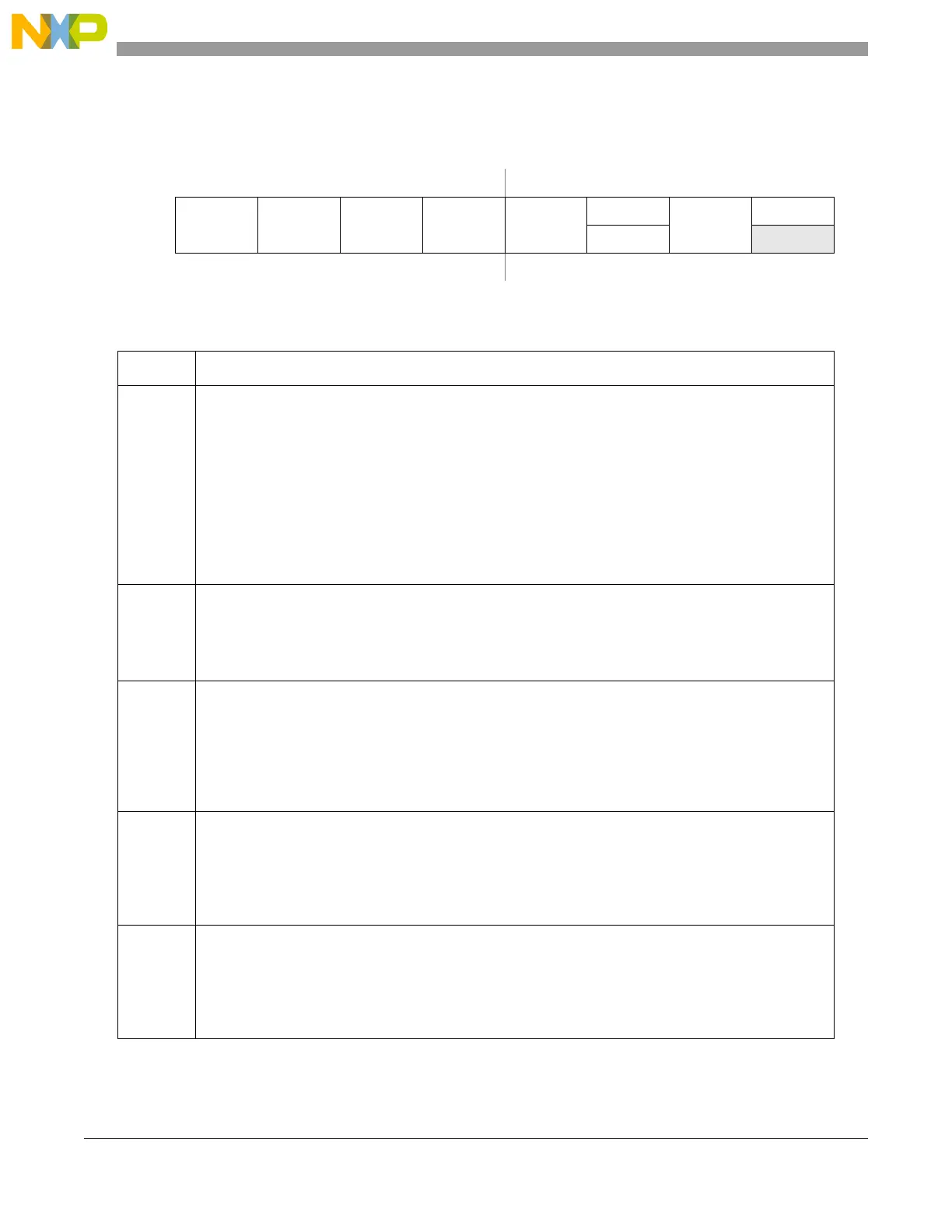

20.3.4 I

2

C Bus Control Register (IBCR)

Offset 0x2 Access: Read/write any time

76543210

R

MDIS IBIE MSSL TXRX NOACK

0

DMAEN

0

WRSTA

Reset10000000

Figure 20-6. I

2

C Bus Control Register (IBCR)

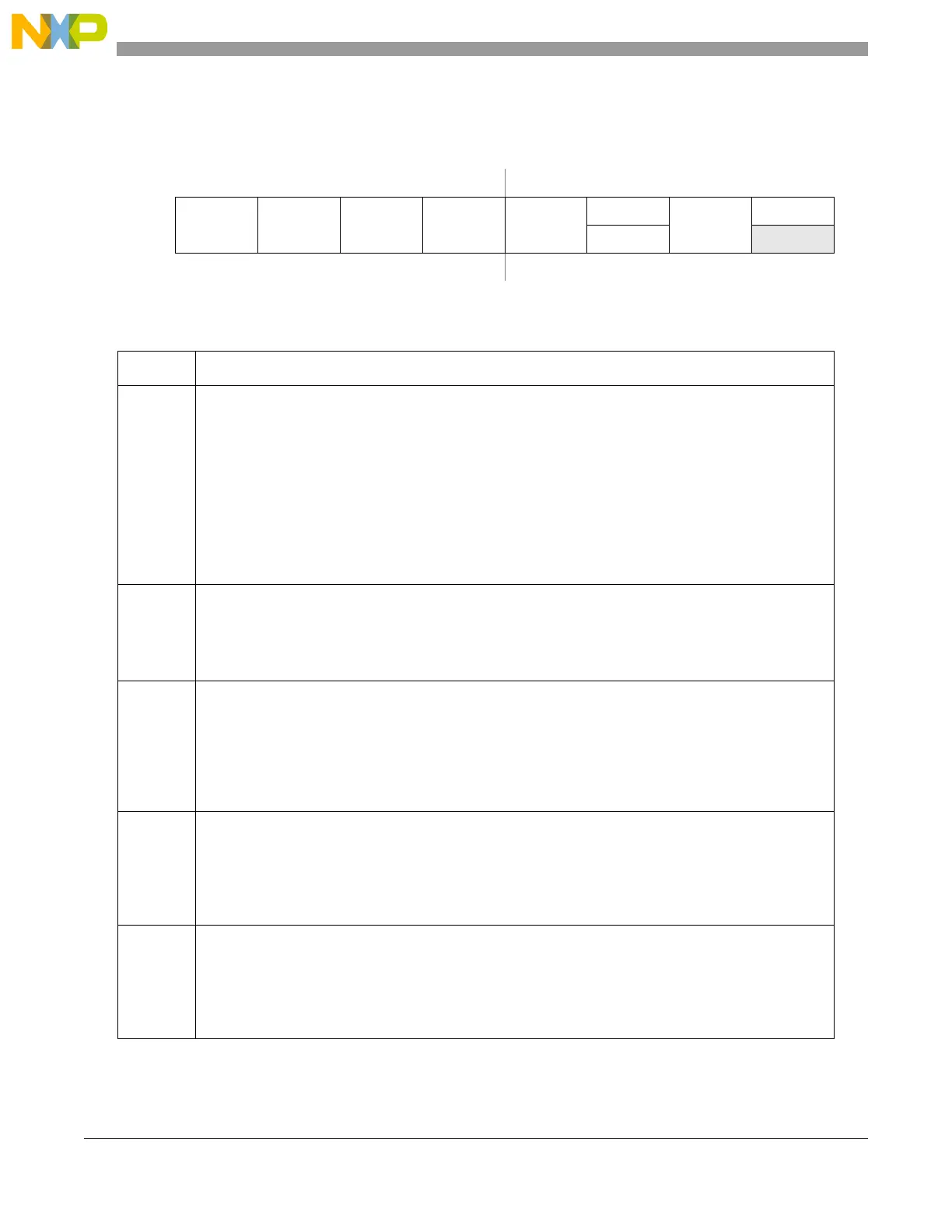

Table 20-8. IBCR field descriptions

Field Description

MDIS Module disable. This bit controls the software reset of the entire I

2

C Bus module.

1 The module is reset and disabled. This is the power-on reset situation. When high, the interface is

held in reset, but registers can still be accessed. Status register bits (IBSR) are not valid when

module is disabled.

0The I

2

C Bus module is enabled. This bit must be cleared before any other IBCR bits have any effect

Note: If the I

2

C Bus module is enabled in the middle of a byte transfer, the interface behaves as follows:

slave mode ignores the current transfer on the bus and starts operating whenever a subsequent

start condition is detected. Master mode will not be aware that the bus is busy, hence if a start

cycle is initiated then the current bus cycle may become corrupt. This would ultimately result in

either the current bus master or the I

2

C Bus module losing arbitration, after which, bus operation

would return to normal.

IBIE I-Bus Interrupt Enable.

1 Interrupts from the I

2

C Bus module are enabled. An I

2

C Bus interrupt occurs provided the IBIF bit in

the status register is also set.

0 Interrupts from the I

2

C Bus module are disabled. Note that this does not clear any currently pending

interrupt condition

MSSL Master/Slave mode select. Upon reset, this bit is cleared. When this bit is changed from 0 to 1, a START

signal is generated on the bus and the master mode is selected. When this bit is changed from 1 to 0,

a STOP signal is generated and the operation mode changes from master to slave. A STOP signal

should be generated only if the IBIF flag is set. MSSL is cleared without generating a STOP signal when

the master loses arbitration.

1 Master Mode

0 Slave Mode

TXRX Transmit/Receive mode select. This bit selects the direction of master and slave transfers. When

addressed as a slave this bit should be set by software according to the SRW bit in the status register.

In master mode this bit should be set according to the type of transfer required. Therefore, for address

cycles, this bit will always be high.

1Transmit

0 Receive

NOACK Data Acknowledge disable. This bit specifies the value driven onto SDA during data acknowledge cycles

for both master and slave receivers. The I

2

C module will always acknowledge address matches,

provided it is enabled, regardless of the value of NOACK. Note that values written to this bit are only

used when the I

2

C Bus is a receiver, not a transmitter.

1 No acknowledge signal response is sent (i.e., acknowledge bit = 1)

0 An acknowledge signal will be sent out to the bus at the 9th clock bit after receiving one byte of data

Loading...

Loading...