MPC5604B/C Microcontroller Reference Manual, Rev. 8

442 Freescale Semiconductor

22.3.4.5 Rx 14 Mask (RX14MASK)

This register is provided for legacy support and for low cost MCUs that do not have the individual masking

per Message Buffer feature. For MCUs supporting individual masks per MB, setting the BCC bit in MCR

causes the RX14MASK Register to have no effect on the module operation.

RX14MASK is used as acceptance mask for the Identifier in Message Buffer 14. When the FEN bit in

MCR is set (FIFO enabled), the RXG14MASK also applies to element 6 of the ID filter table. This register

has the same structure as the Rx Global Mask Register.

Refer to Section 22.4.8, “Rx FIFO for important details on usage of RX14MASK on filtering process for

Rx FIFO.

It must be programmed while the module is in Freeze Mode, and must not be modified when the module

is transmitting or receiving frames.

• Address Offset: 0x14

• Reset Value: 0xFFFF_FFFF

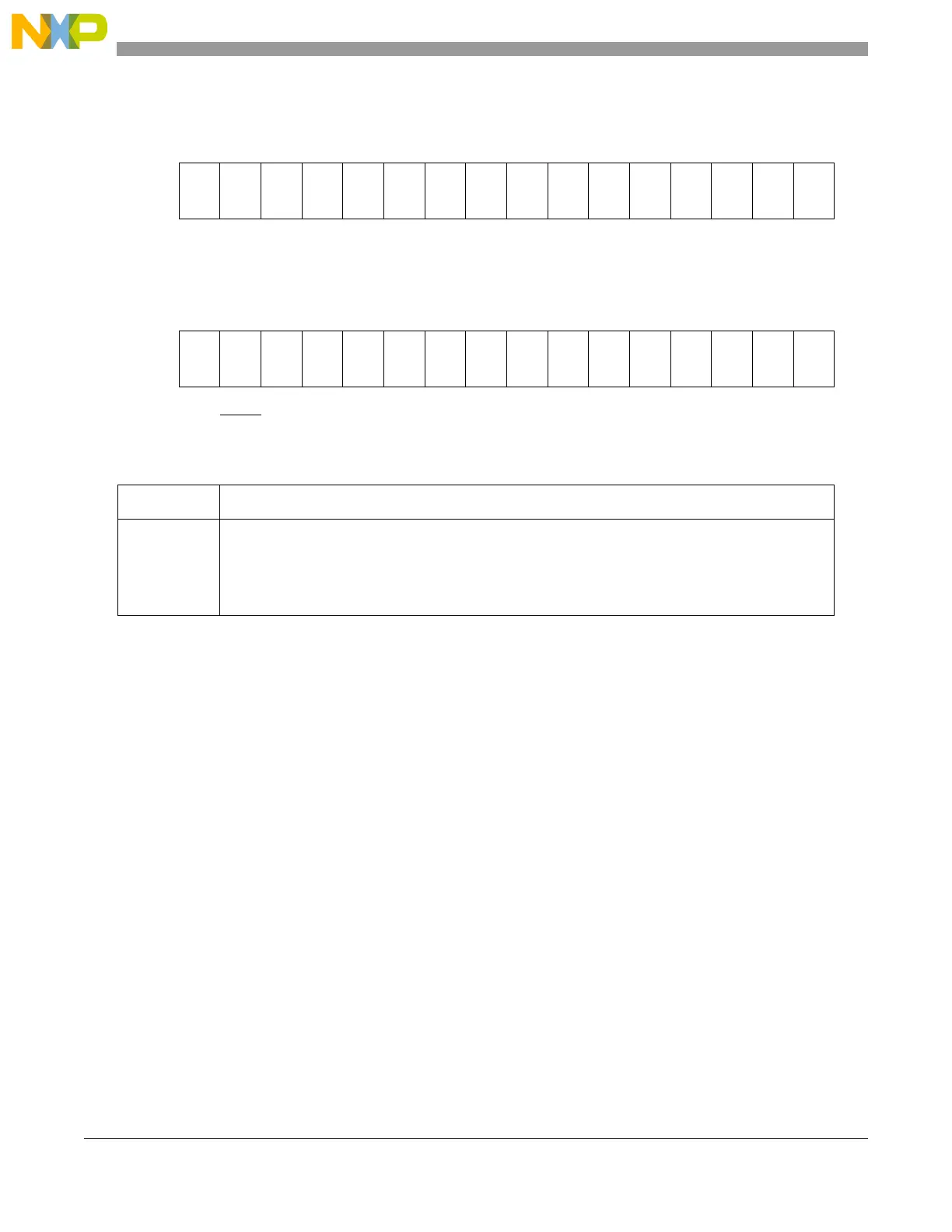

Offset: 0x0010 Access: Read/write

0123456789101112131415

R

MI31 MI30 MI29 MI28 MI27 MI26 MI25 MI24 MI23 MI22 MI21 MI20 MI19 MI18 MI17 MI16

W

Reset1111111111111111

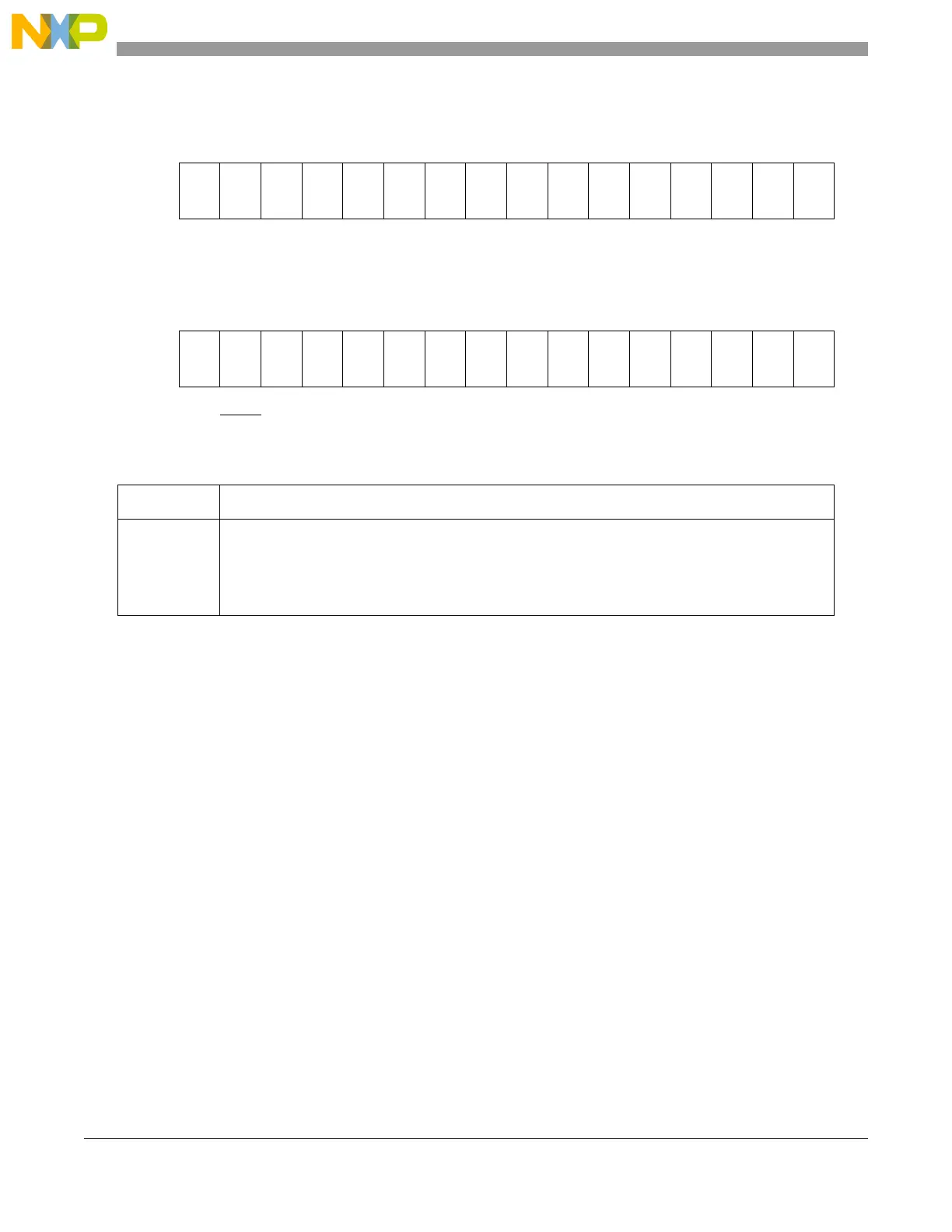

16 17 18 19 20 21 22 23 24 25 26 27 28 29 30 31

R

MI15 MI14 MI13 MI12 MI11 MI10 MI9 MI8 MI7 MI6 MI5 MI4 MI3 MI2 MI1 MI0

W

Reset1111111111111111

Figure 22-8. Rx Global Mask Register (RXGMASK)

Table 22-11. RXGMASK field description

Field Description

MI31–MI0 Mask Bits

For normal Rx MBs, the mask bits affect the ID filter programmed on the MB. For the Rx FIFO, the

mask bits affect all bits programmed in the filter table (ID, IDE, RTR).

1 = The corresponding bit in the filter is checked against the one received

0 = the corresponding bit in the filter is “don’t care”

Loading...

Loading...