MPC5604B/C Microcontroller Reference Manual, Rev. 8

480 Freescale Semiconductor

CPHA Clock Phase

The CPHA bit selects which edge of SCK causes data to change and which edge causes data to be

captured. This bit is used in both Master and Slave Mode. For successful communication between

serial devices, the devices must have identical clock phase settings. Continuous SCK is only

supported for CPHA = 1.

0 Data is captured on the leading edge of SCK and changed on the following edge

1 Data is changed on the leading edge of SCK and captured on the following edge

LSBFE LSB First

The LSBFE bit selects if the LSB or MSB of the frame is transferred first. This bit is only used in Master

Mode.

0 Data is transferred MSB first

1 Data is transferred LSB first

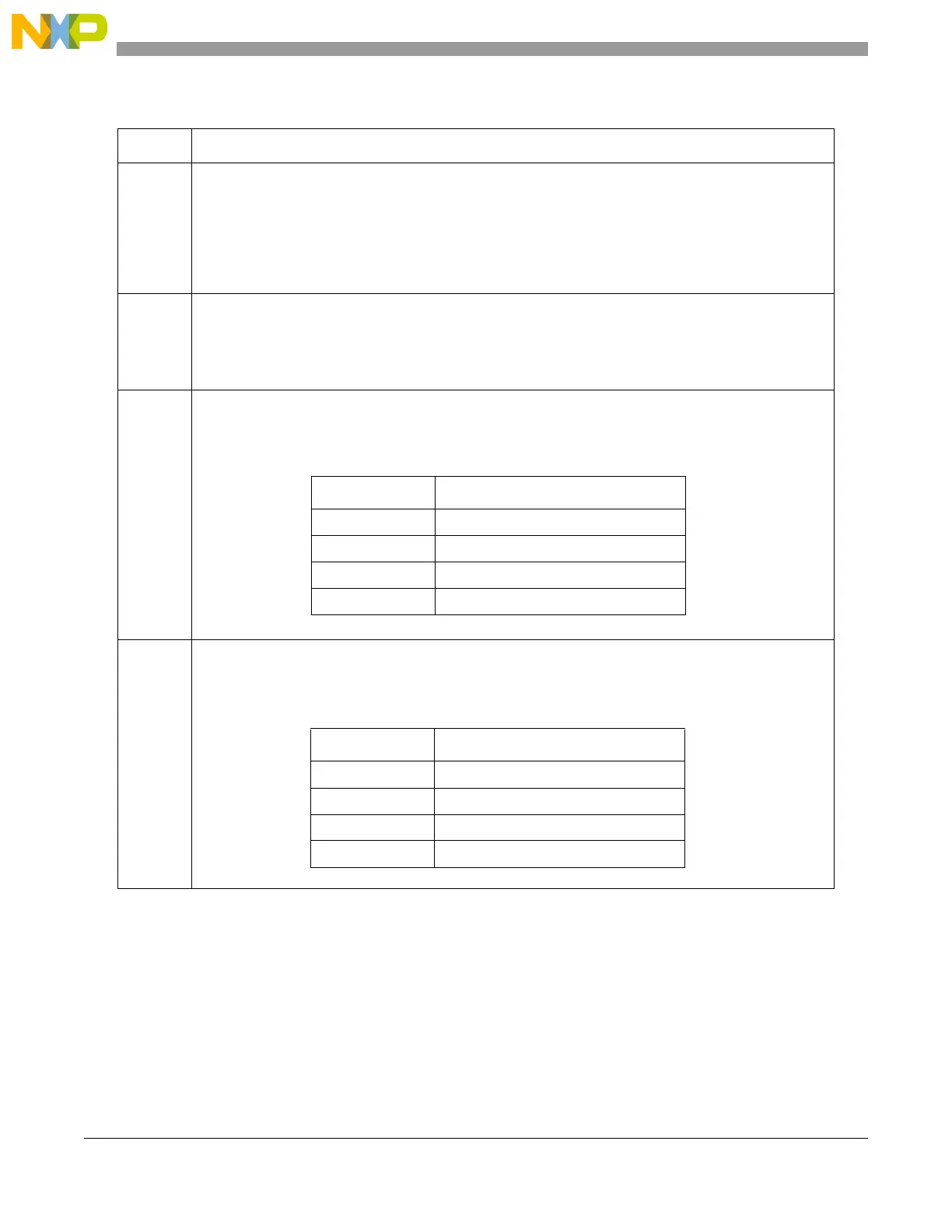

PCSSCK PCS to SCK Delay Prescaler

The PCSSCK field selects the prescaler value for the delay between assertion of PCS and the first edge

of the SCK. This field is only used in Master Mode. The table below lists the prescaler values. See the

CSSCK field description for details on how to compute the PCS to SCK delay.

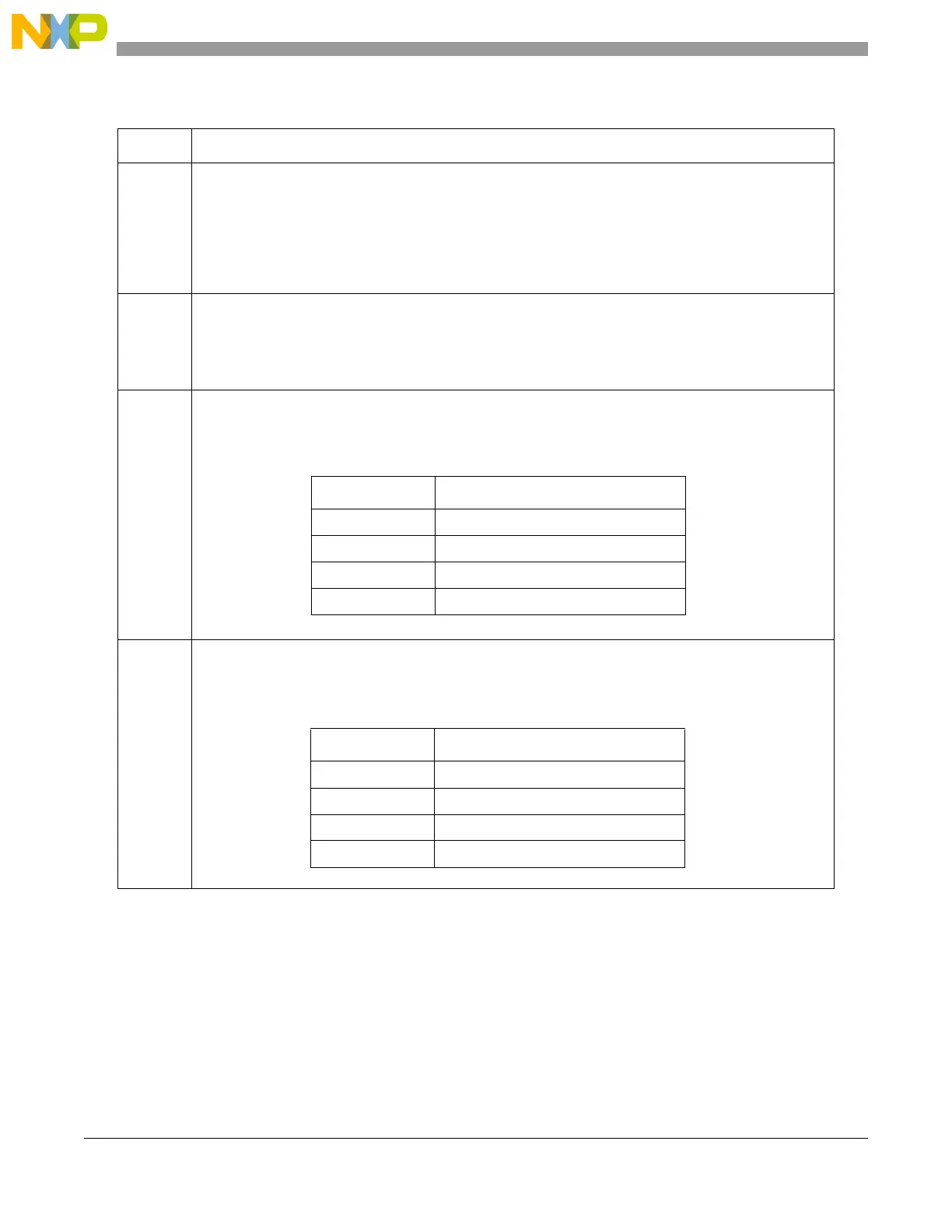

PASC After SCK Delay Prescaler

The PASC field selects the prescaler value for the delay between the last edge of SCK and the negation

of PCS. This field is only used in Master Mode. The table below lists the prescaler values. See the

ASC[0:3] field description for details on how to compute the After SCK delay.

Table 23-5. DSPIx_CTARn field descriptions (continued)

Field Descriptions

PCSSCK PCS to SCK delay prescaler value

00 1

01 3

10 5

11 7

PASC After SCK delay prescaler value

00 1

01 3

10 5

11 7

Loading...

Loading...