MPC5604B/C Microcontroller Reference Manual, Rev. 8

Freescale Semiconductor 531

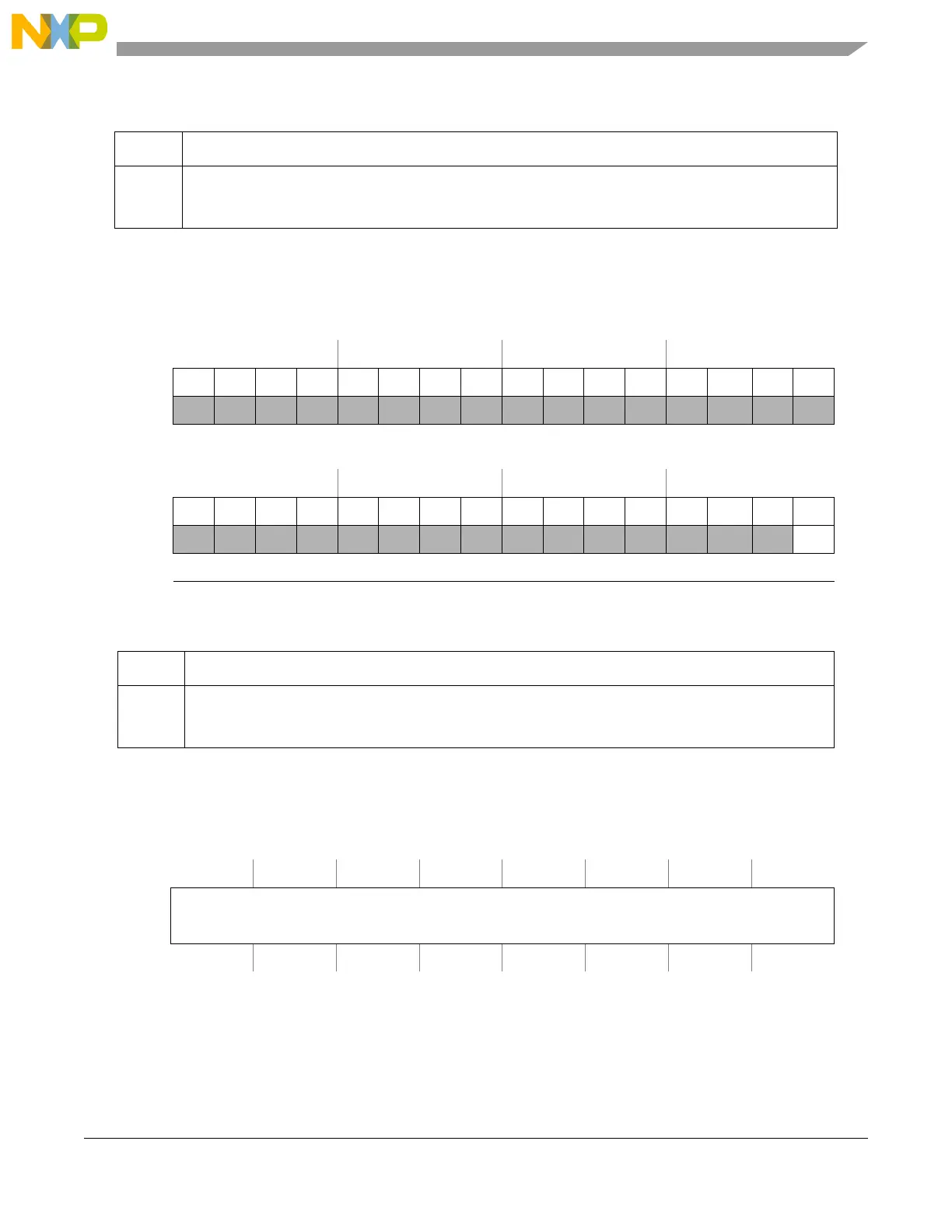

24.3.3.2.4 STM Channel Interrupt Register (STM_CIRn)

The STM Channel Interrupt Register (STM_CIRn) has the interrupt flag for channel n of the timer.

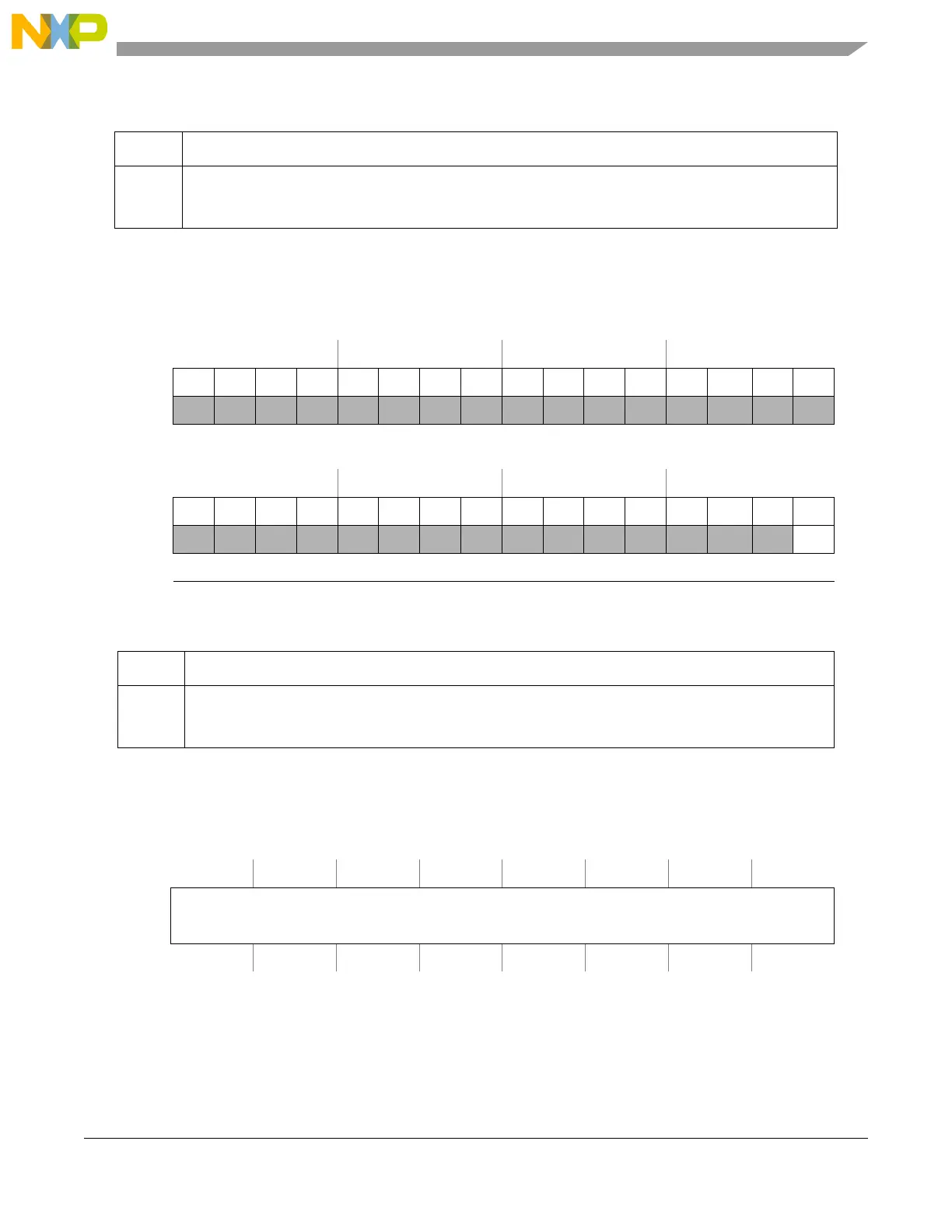

24.3.3.2.5 STM Channel Compare Register (STM_CMPn)

The STM channel compare register (STM_CMPn) holds the compare value for channel n.

Table 24-6. STM_CCRn field descriptions

Field Description

CEN Channel Enable.

0 = The channel is disabled.

1 = The channel is enabled.

Offset: 0x14+0x10*n Access: Read/Write

0123456789101112131415

R 0 0 0 0 0 00000000 0 00

W

Reset0000000000000 0 00

16 17 18 19 20 21 22 23 24 25 26 27 28 29 30 31

R 0 000000000 0

0

000CIF

W w1c

Reset0000000000000 0 00

Figure 24-5. STM Channel Interrupt Register (STM_CIRn)

Table 24-7. STM_CIRn field descriptions

Field Description

CIF Channel Interrupt Flag

0 = No interrupt request.

1 = Interrupt request due to a match on the channel.

Offset: 0x18+0x10*n Access: Read/Write

012345678910111213141516171819202122232425262728293031

R

CMP

W

Reset00000000000000000000000000000000

Figure 24-6. STM Channel Compare Register (STM_CMPn)

Loading...

Loading...