MPC5604B/C Microcontroller Reference Manual, Rev. 8

530 Freescale Semiconductor

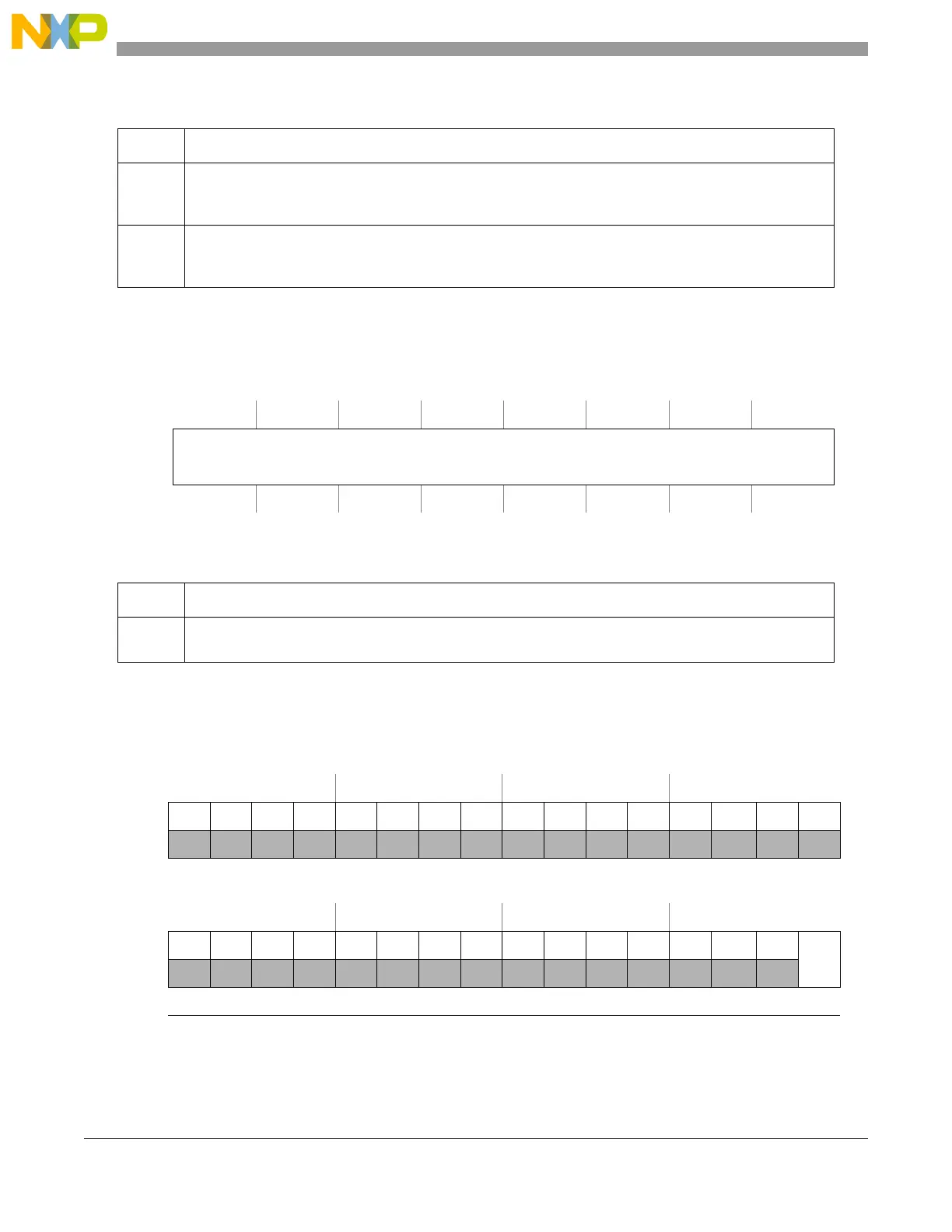

24.3.3.2.2 STM Count Register (STM_CNT)

The STM Count Register (STM_CNT) holds the timer count value.

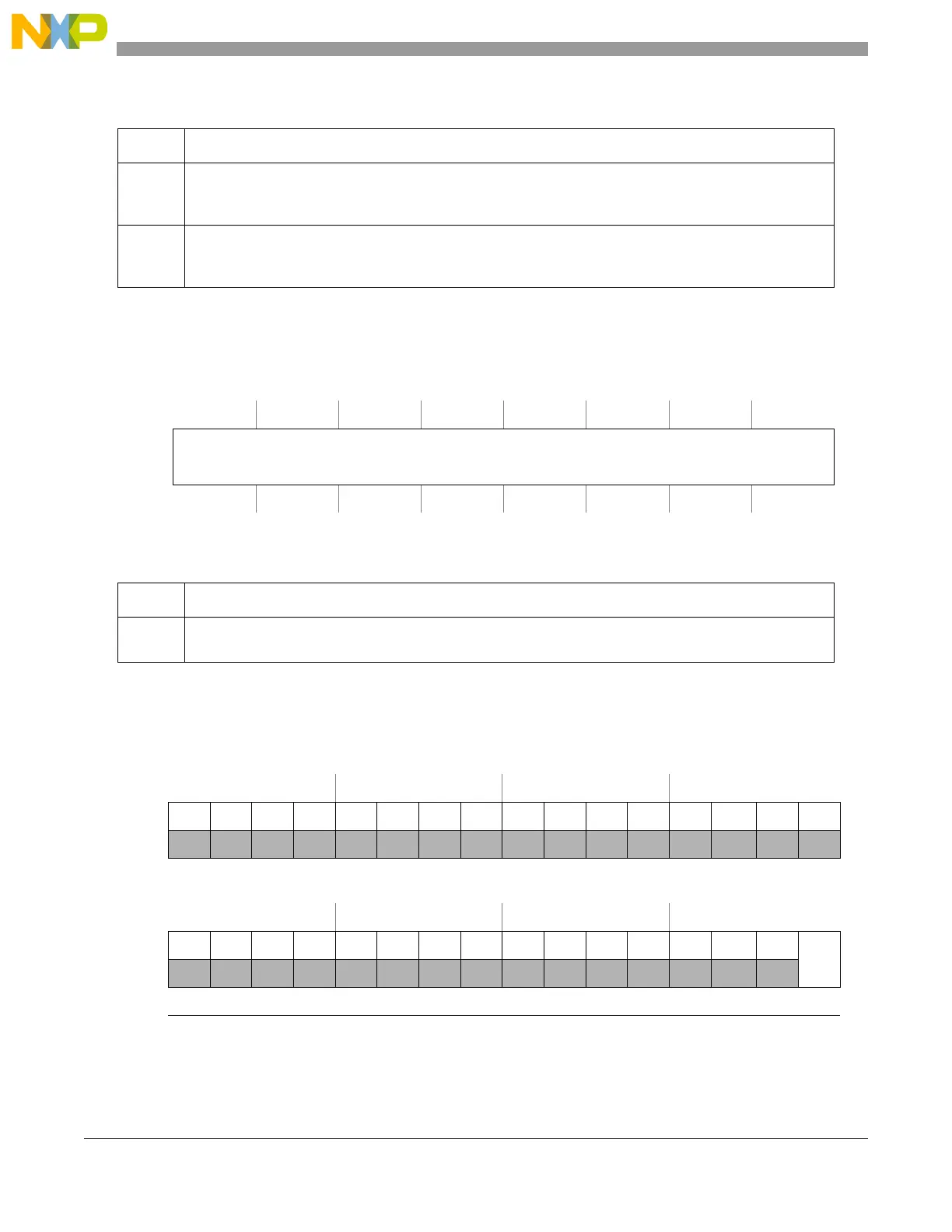

24.3.3.2.3 STM Channel Control Register (STM_CCRn)

The STM Channel Control Register (STM_CCRn) has the enable bit for channel n of the timer.

FRZ Freeze. Allows the timer counter to be stopped when the device enters debug mode.

0 = STM counter continues to run in debug mode.

1 = STM counter is stopped in debug mode.

TEN Timer Counter Enabled.

0 = Counter is disabled.

1 = Counter is enabled.

Offset: 0x004 Access: Read/Write

012345678910111213141516171819202122232425262728293031

R

CNT

W

Reset00000000000000000000000000000000

Figure 24-3. STM Count Register (STM_CNT)

Table 24-5. STM_CNT field descriptions

Field Description

CNT Timer count value used as the time base for all channels. When enabled, the counter increments at the

rate of the system clock divided by the prescale value.

Offset: 0x10+0x10*n Access: Read/Write

0123456789101112131415

R 0 0 0 0 0 00000000 0 00

W

Reset0000000000000 0 00

16 17 18 19 20 21 22 23 24 25 26 27 28 29 30 31

R 0 000000000 0

0

000

CEN

W

Reset0000000000000 0 00

Figure 24-4. STM Channel Control Register (STM_CCRn)

Table 24-4. STM_CR field descriptions

Field Description

Loading...

Loading...