MPC5604B/C Microcontroller Reference Manual, Rev. 8

538 Freescale Semiconductor

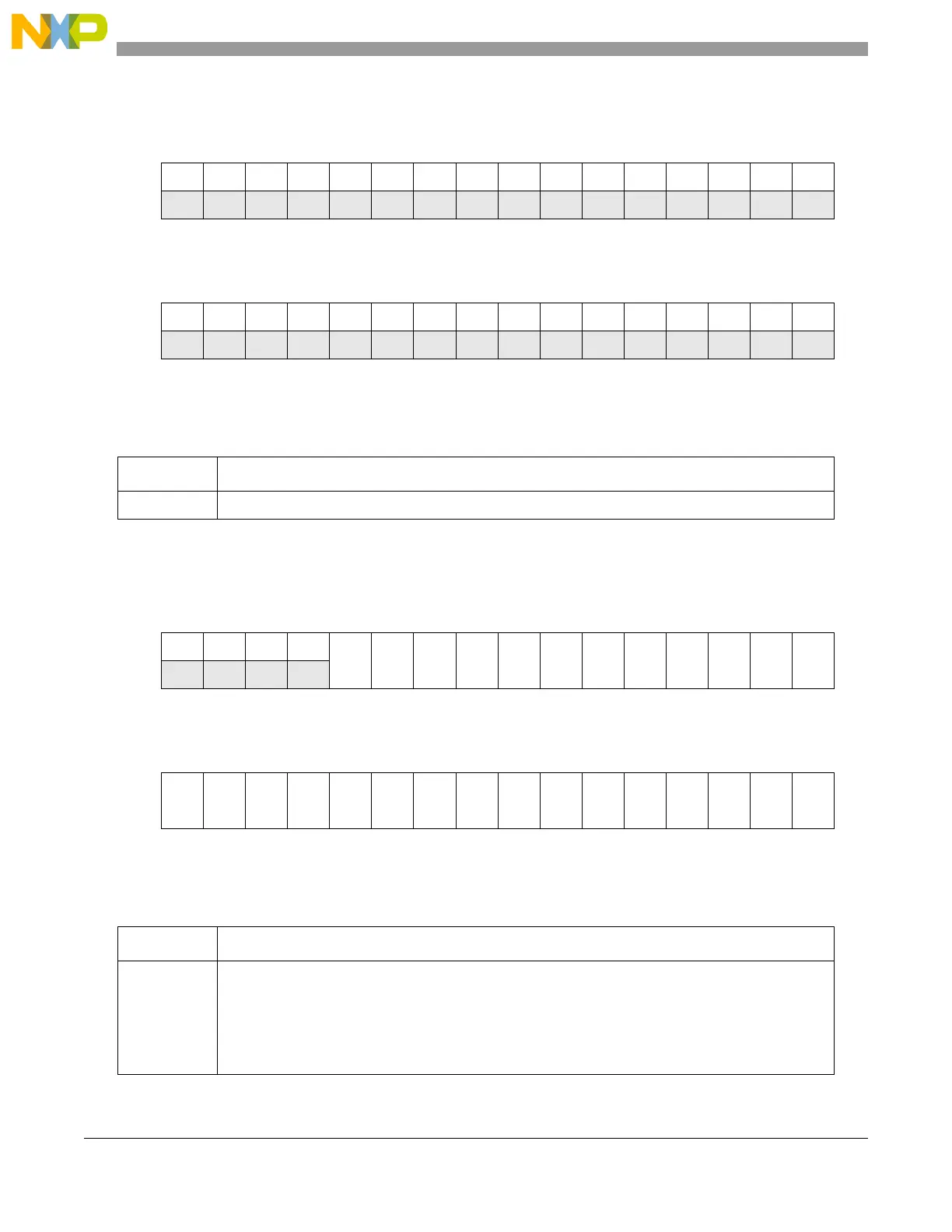

24.4.3.2.3 eMIOS Output Update Disable (EMIOSOUDIS) Register

Address: eMIOS base address +0x04

0123456789101112131415

R 0 0 0 0 F27 F26 F25 F24 F23 F22 F21 F20 F19 F18 F17 F16

W

Reset0000000000000000

16 17 18 19 20 21 22 23 24 25 26 27 28 29 30 31

RF15F14F13F12F11F10F9F8F7F6F5F4F3F2F1F0

W

Reset0000000000000000

Figure 24-9. eMIOS Global FLAG (EMIOSGFLAG) Register

Table 24-13. EMIOSGFLAG field descriptions

Field Description

Fn Channel [n] Flag bit

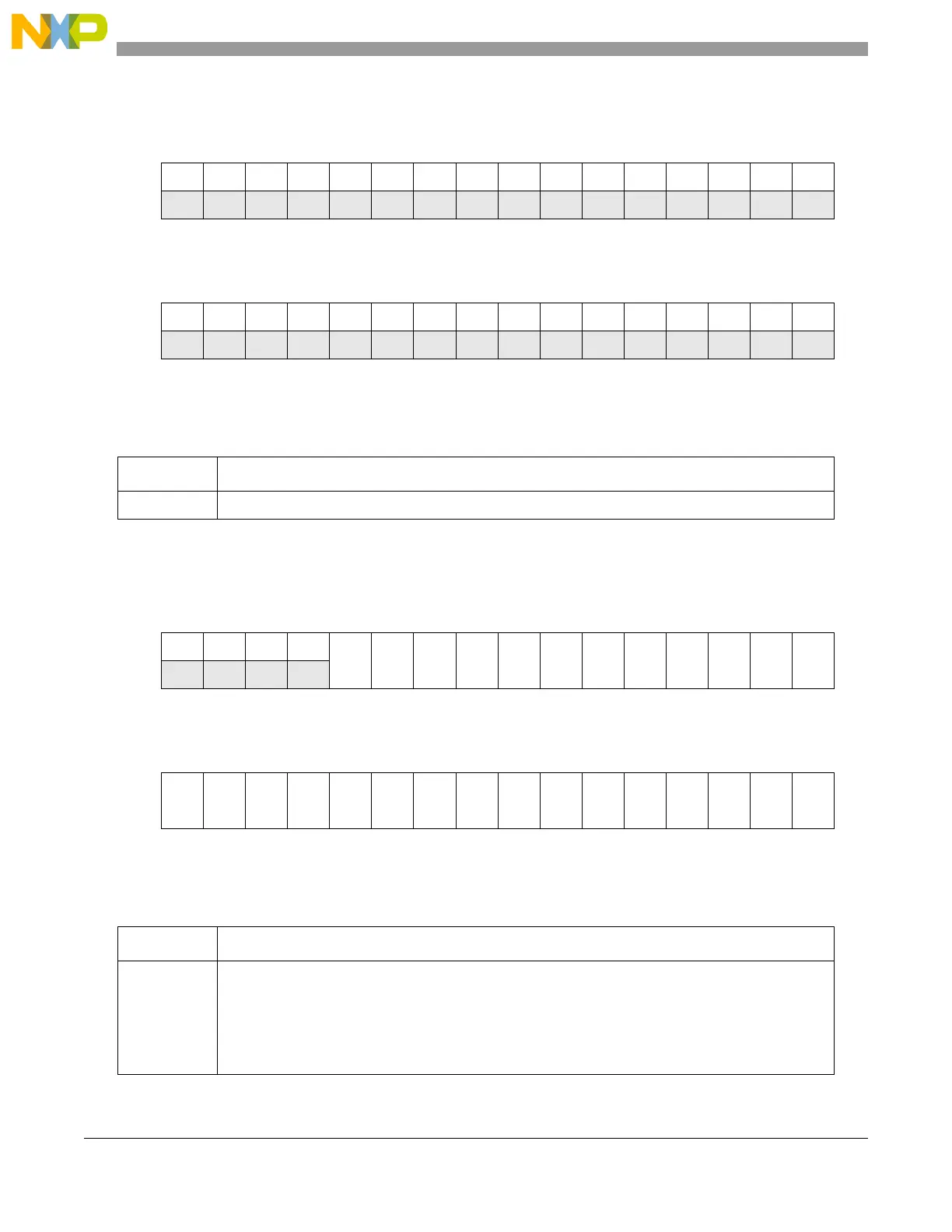

Address: eMIOS base address +0x08

0123456789101112131415

R0000

OU27

OU26

OU25

OU24

OU23

OU22

OU21

OU20

OU19

OU18

OU17

OU16

W

Reset0000000000000000

16 17 18 19 20 21 22 23 24 25 26 27 28 29 30 31

R

OU15

OU14

OU13

OU12

OU11

OU10

OU9 OU8 OU7 OU6 OU5 OU4 OU3 OU2 OU1 OU0

W

Reset0000000000000000

Figure 24-10. eMIOS Output Update Disable (EMIOSOUDIS) Register

Table 24-14. EMIOSOUDIS field descriptions

Field Description

OUn Channel [n] Output Update Disable bit

When running MC, MCB or an output mode, values are written to registers A2 and B2. OU[n] bits

are used to disable transfers from registers A2 to A1 and B2 to B1. Each bit controls one channel.

1 = Transfers disabled

0 = Transfer enabled. Depending on the operation mode, transfer may occur immediately or in the

next period. Unless stated otherwise, transfer occurs immediately.

Loading...

Loading...