MPC5604B/C Microcontroller Reference Manual, Rev. 8

632 Freescale Semiconductor

26.4.1 Event Configuration Registers (CTU_EVTCFGRx) (x = 0...63)

These registers contain the ADC channel number to be converted when the timer event occurs. The

CLR_FLAG is used to clear the respective timer event flag by software (this applies only to the PIT as the

eMIOS flags are automatically cleared by the CTU).

The CLR_FLAG bit has to be used cautiously as setting this bit may result in a loss of events.

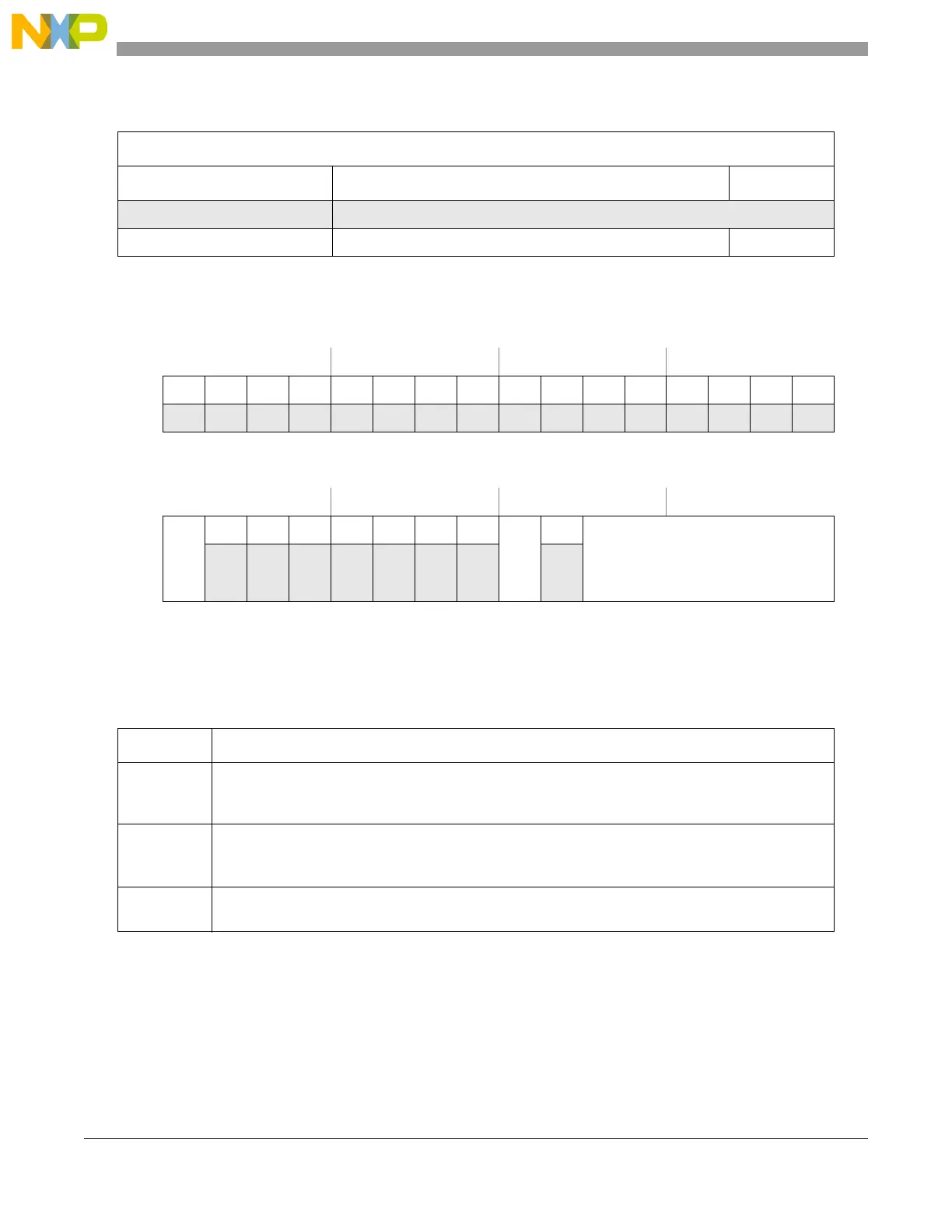

Table 26-1. CTU memory map

Base address: 0xFFE6_4000

Address offset Register Location

0x000–0x02F Reserved

0x030–0x12C Event Configuration Registers 0..63 (CTU_EVTCFGR0..63) on page 632

Offsets: 0x030–0x12C Access: Read/write

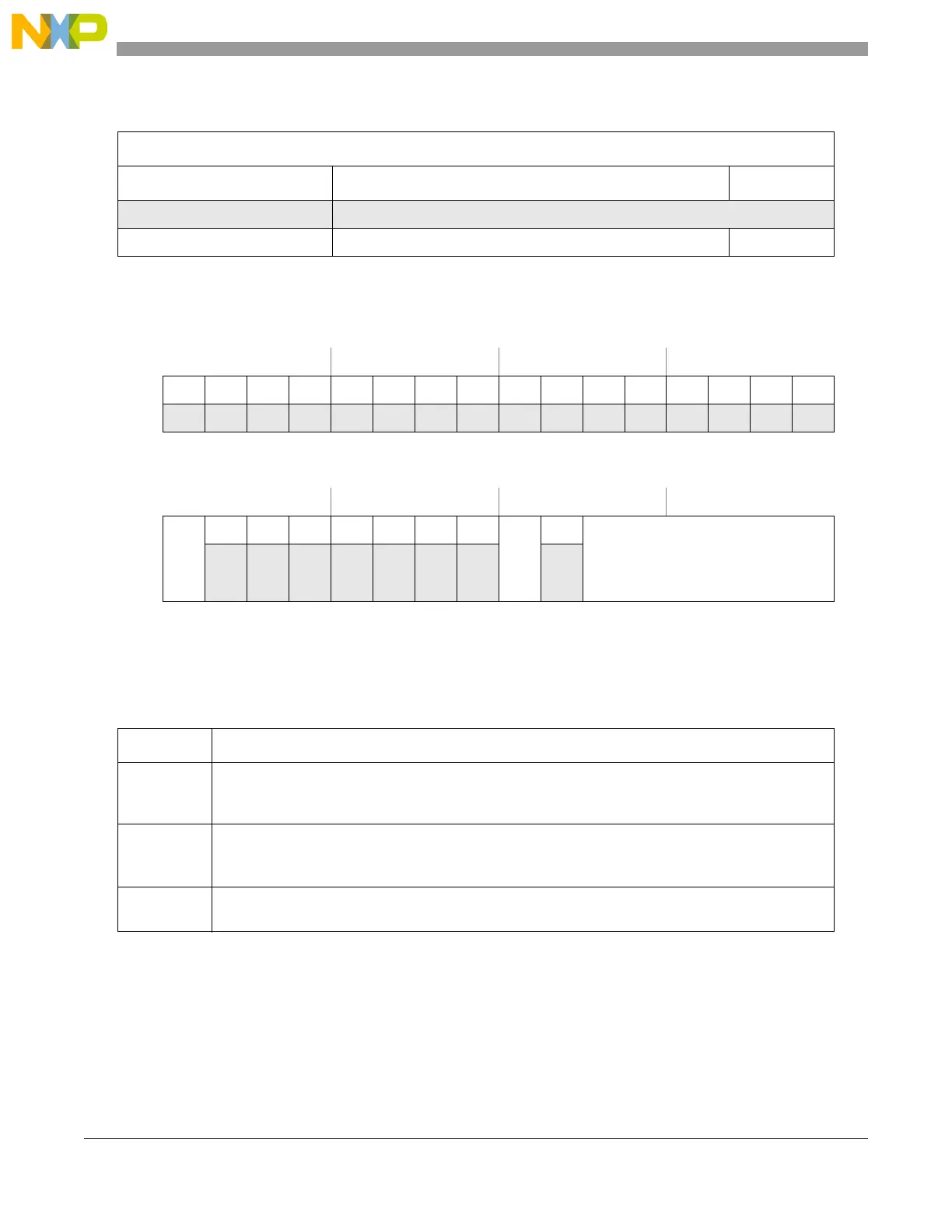

0123456789101112131415

R0000000000000000

W

Reset0000000000000000

16 17 18 19 20 21 22 23 24 25 26 27 28 29 30 31

R

TM

0000000

CLR_FLAG

1

1

This bit implementation is generic based and implemented only for inputs mapped to PIT event flags.

0

CHANNEL_VALUE

W

Reset0000000000000000

Figure 26-2. Event Configuration Registers (CTU_EVTCFGRx) (x = 0...63)

Table 26-2. CTU_EVTCFGRx field descriptions

Field Description

TM Trigger Mask

0: Trigger masked

1: Trigger enabled

CLR_FLAG To provide flag_ack through software

1: Flag_ack is forced to ‘1’ for the particular event

0: Flag_ack is dependent on flag servicing

CHANNEL_

VALUE

Channel value to be provided to ADC

Loading...

Loading...