MPC5604B/C Microcontroller Reference Manual, Rev. 8

662 Freescale Semiconductor

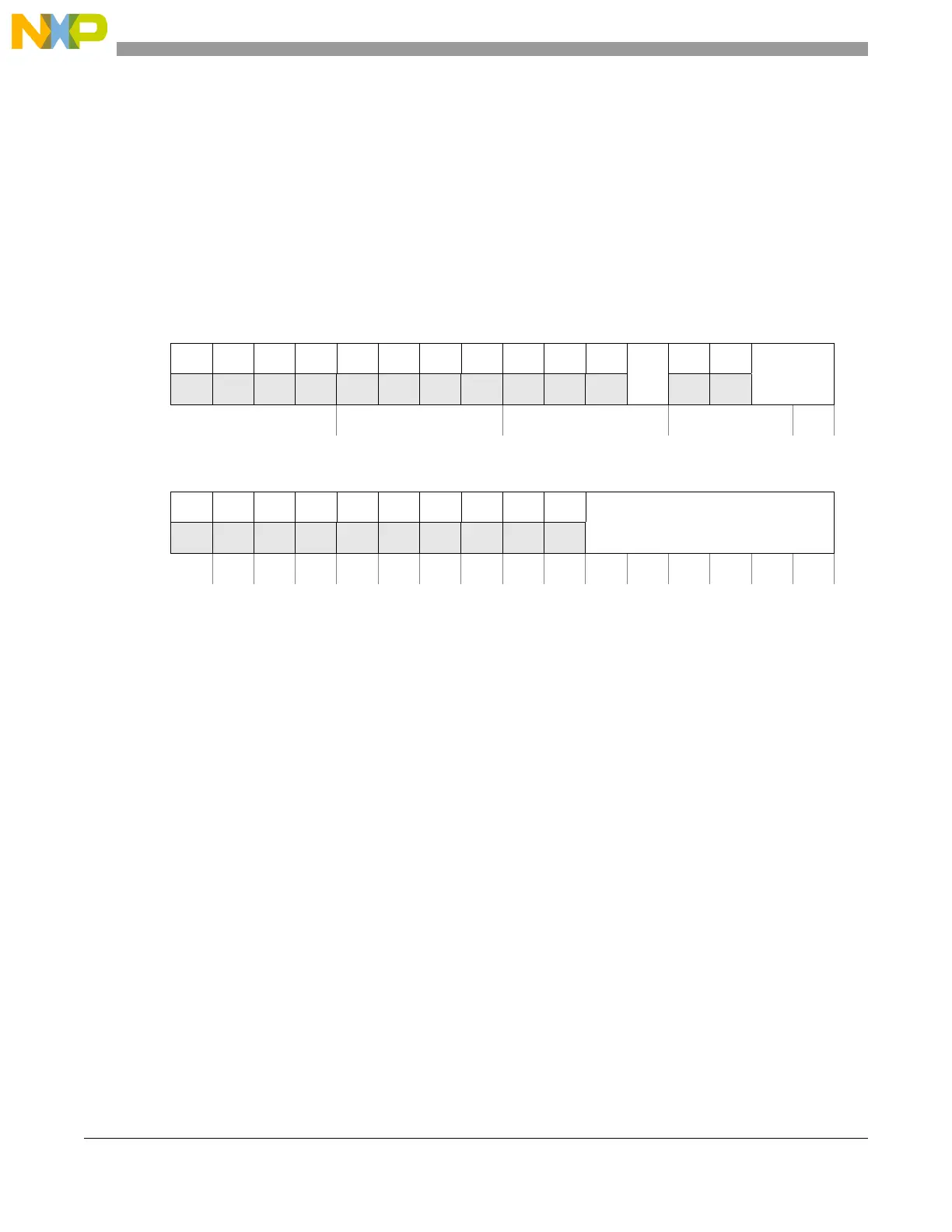

27.5.1.3.1 CFlash Nonvolatile Secondary Low/Mid Address Space Block Locking

Register (CFLASH_NVSLL)

The CFLASH_SLL register has a related Nonvolatile Secondary Low/Mid Address Space Block Locking

register located in TestFlash that contains the default reset value for SLL. During the reset phase of the

flash memory module, the CFLASH_NVSLL register content is read and loaded into the CFLASH_SLL.

The CFLASH_NVSLL register is a 64-bit register, of which the 32 most significant bits 63:32 are ‘don’t

care’ and are used to manage ECC codes.

Offset: 0x403DF8 Access: Read/write

0123456789101112131415

R

SLE1111111111

STSLK

11

SMK

W

Reset

1111111111111111

16 17 18 19 20 21 22 23 24 25 26 27 28 29 30 31

R

1111111111

SLK

W

Reset

1111111111111111

Figure 27-7. CFlash Nonvolatile Secondary Low/mid address space block Locking register

(CFLASH_NVSLL)

Loading...

Loading...