MPC5604B/C Microcontroller Reference Manual, Rev. 8

Freescale Semiconductor 669

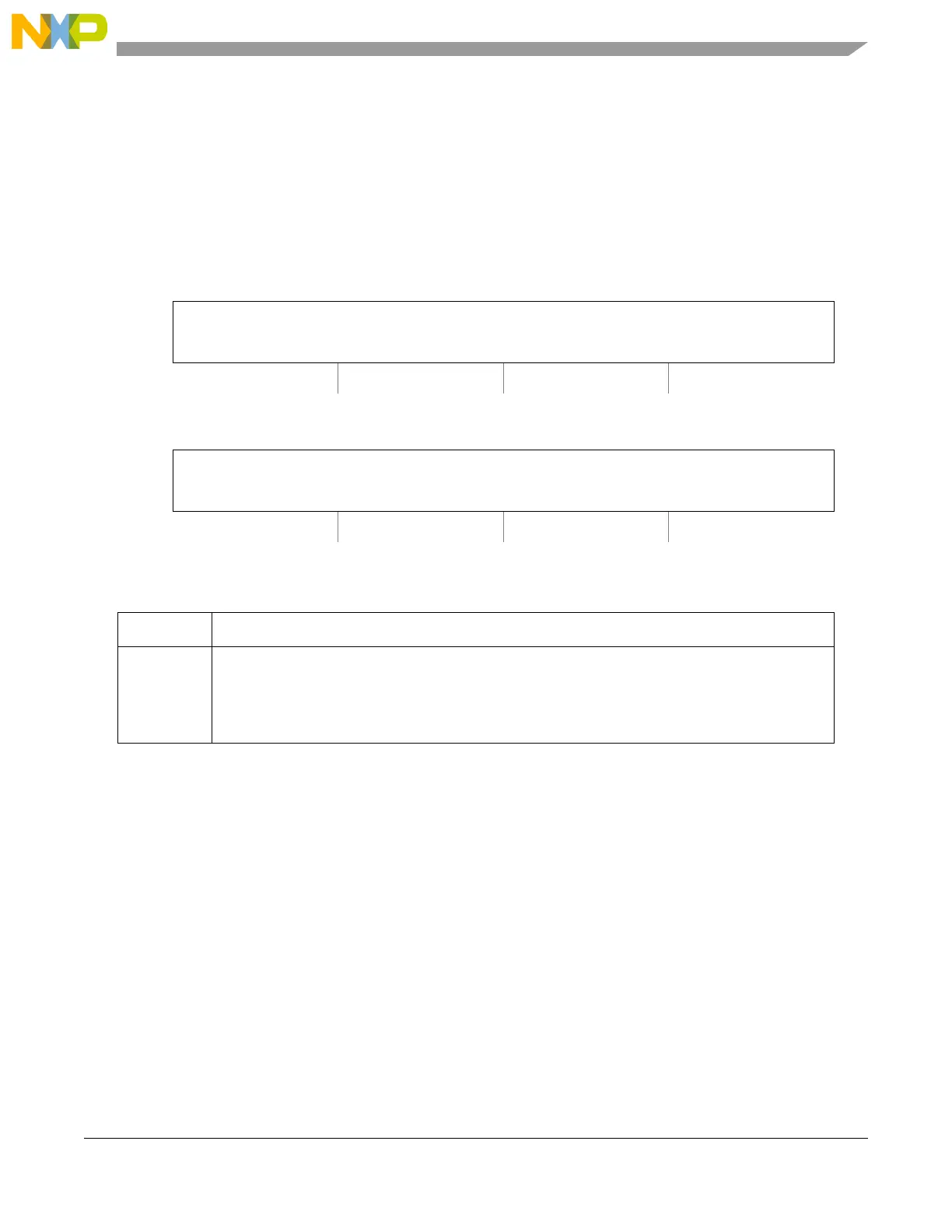

27.5.1.7 CFlash User Test 1 register (CFLASH_UT1)

The CFLASH_UT1 register allows to enable the checks on the ECC logic related to the 32 LSB of the

Double Word.

The User Test 1 Register is not accessible whenever CFLASH_MCR[DONE] or CFLASH_UT0[AID] are

low: reading returns indeterminate data while writing has no effect.

27.5.1.8 CFlash User Test 2 register (CFLASH_UT2)

The CFLASH_UT2 register allows to enable the checks on the ECC logic related to the 32 MSB of the

Double Word.

The User Test 2 Register is not accessible whenever CFLASH_MCR[DONE] or CFLASH_UT0[AID] are

low: reading returns indeterminate data while writing has no effect.

Offset: 0x00040 Access: Read/write

0123456789101112131415

R

DAI[31:16]

W

Reset

0000000000000000

16 17 18 19 20 21 22 23 24 25 26 27 28 29 30 31

R

DAI[15:0]

W

Reset

0000000000000000

Figure 27-11. CFlash User Test 1 register (CFLASH_UT1)

Table 27-22. CFLASH_UT1 field descriptions

Field Description

DAI[31:0] Data Array Input, bits 31–0

These bits represent the input of even word of ECC logic used in the ECC Logic Check. Bits

DAI[31:00] correspond to the 32 array bits representing Word 0 within the double word.

0: The array bit is forced at 0.

1: The array bit is forced at 1.

Loading...

Loading...