MPC5604B/C Microcontroller Reference Manual, Rev. 8

Freescale Semiconductor 715

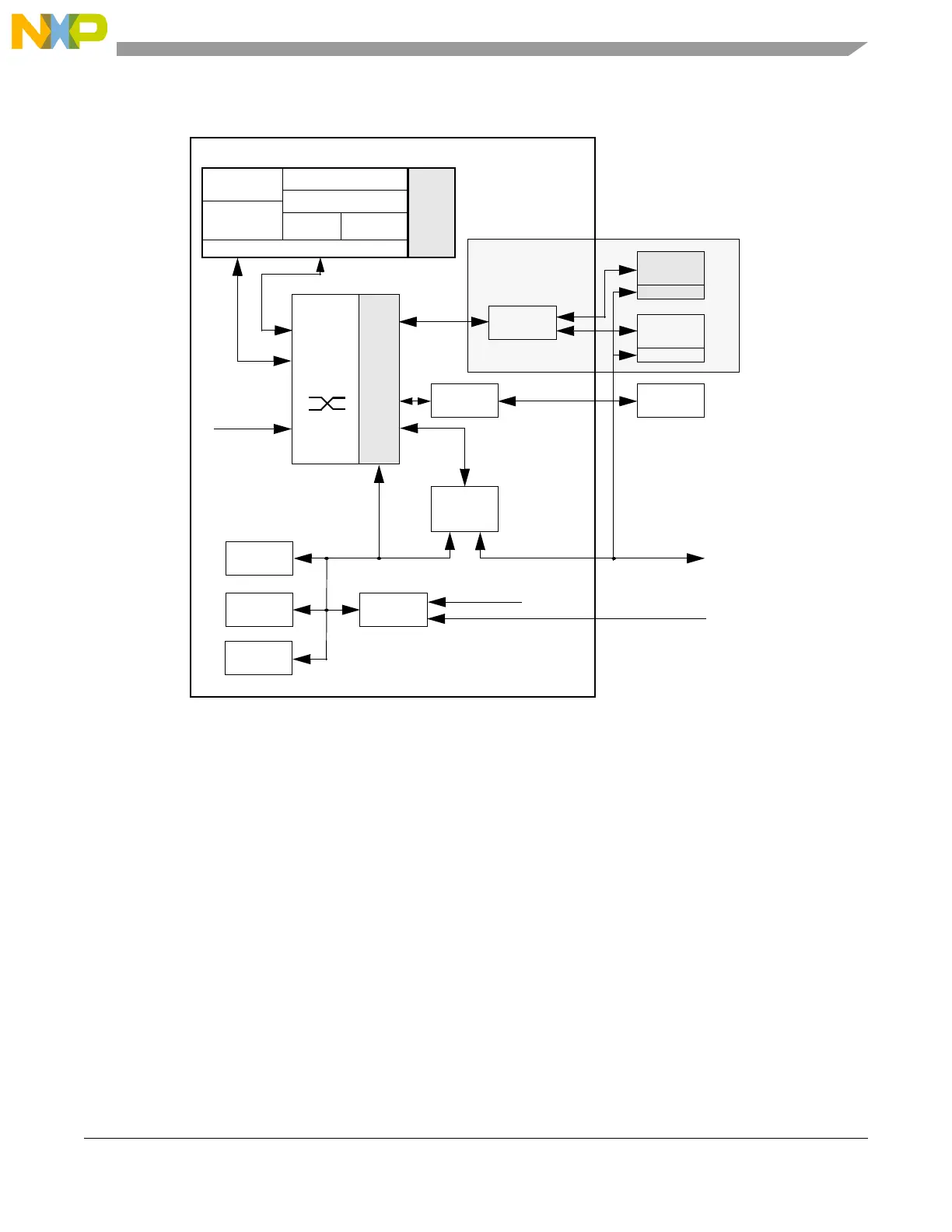

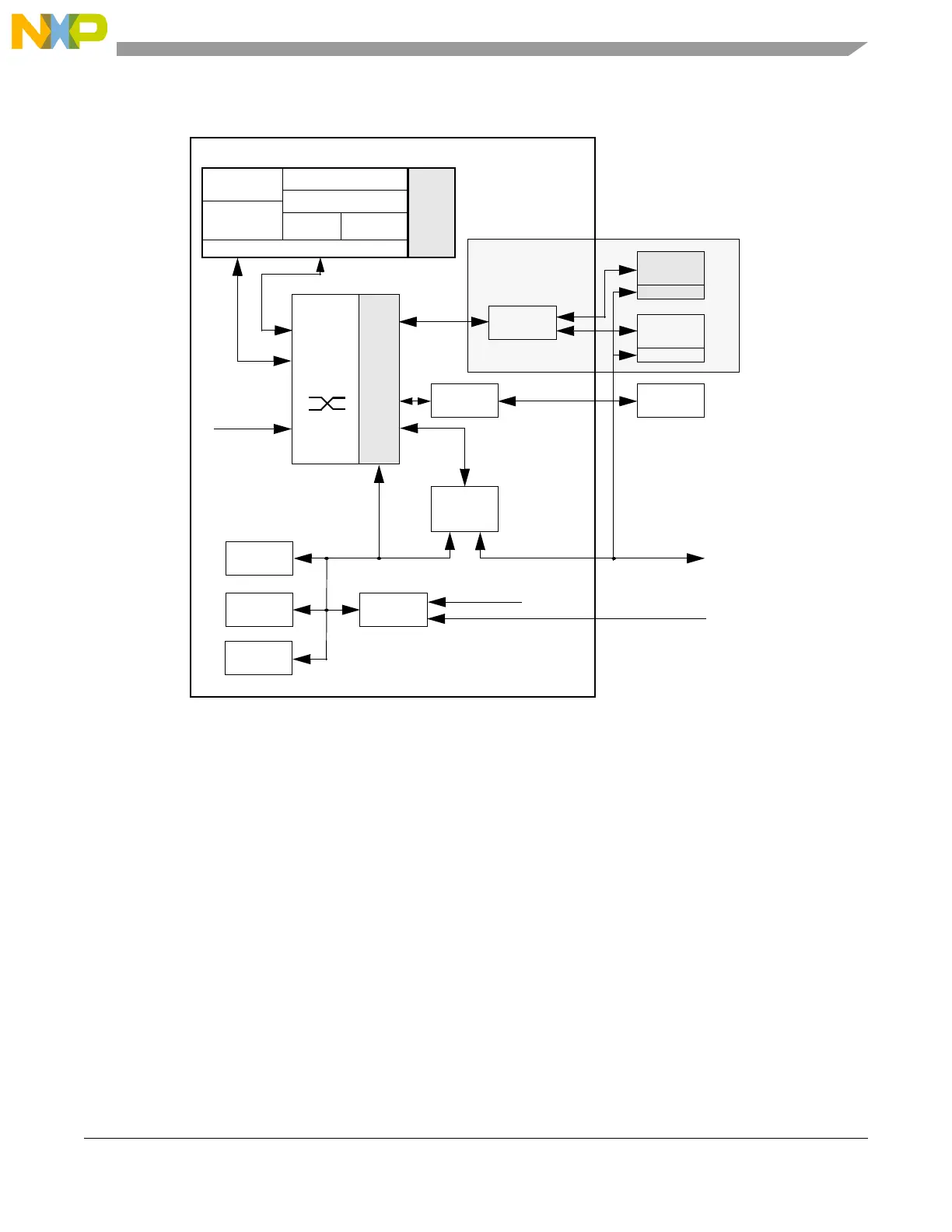

Figure 27-38. Power Architecture e200z0h RPP reference platform block diagram

The module list includes:

• Power Architecture e200z0h (Harvard) core with Nexus1 or optional Nexus2+ debug

• AHB crossbar switch “lite” (XBAR)

• Memory Protection Unit (MPU)

• Platform flash memory controller with connections to 2 memory banks

• Platform SRAM memory controller (PRAM)

• AHB-to-IPS/APB bus controller (PBRIDGE) for access to on- and off-platform slave modules

• Interrupt Controller (INTC)

• 4-channel System Timers (STM)

• Software Watchdog Timer (SWT)

• Error Correction Status Module (ECSM)

XBAR

MemArray

RPP_Z0H_REF

s0

s2

m0

s7

MemArray

PRAM

PFlash

IPS/APB

INTC

AHB platform flash memory controller

Branch Unit

Load/Store

I-Fetcher

Dispatch

GPR

Integer

Unit

e200z0h Core

p_i_h*

p_d_h*

m1

m2

MPU

On-platform IRQs

Off-Platform IRQs

Debug

Unit

Nexus1,

Nexus2+

m3

STM

IPS Bus

IPS+APB Bus

Flash Regs

IPS+APB

Slave

Modules

MemArray

Flash Regs

Bank0

Bank1

ECSM

SWT

Loading...

Loading...