MPC5604B/C Microcontroller Reference Manual, Rev. 8

Freescale Semiconductor 725

27.7.2.2.3.1 Nonvolatile Platform Flash Access Protection Register (NVPFAPR)

The NVPFAPR register has a related Nonvolatile PFAPR located in the Shadow Sector that contains the

default reset value for PFAPR. During the reset phase of the flash memory module, the NVPFAPR register

content is read and loaded into the PFAPR.

The NVPFAPR register is a 64-bit register, of which the 32 most significant bits 63:32 are ‘don’t care’ and

are used to manage ECC codes.

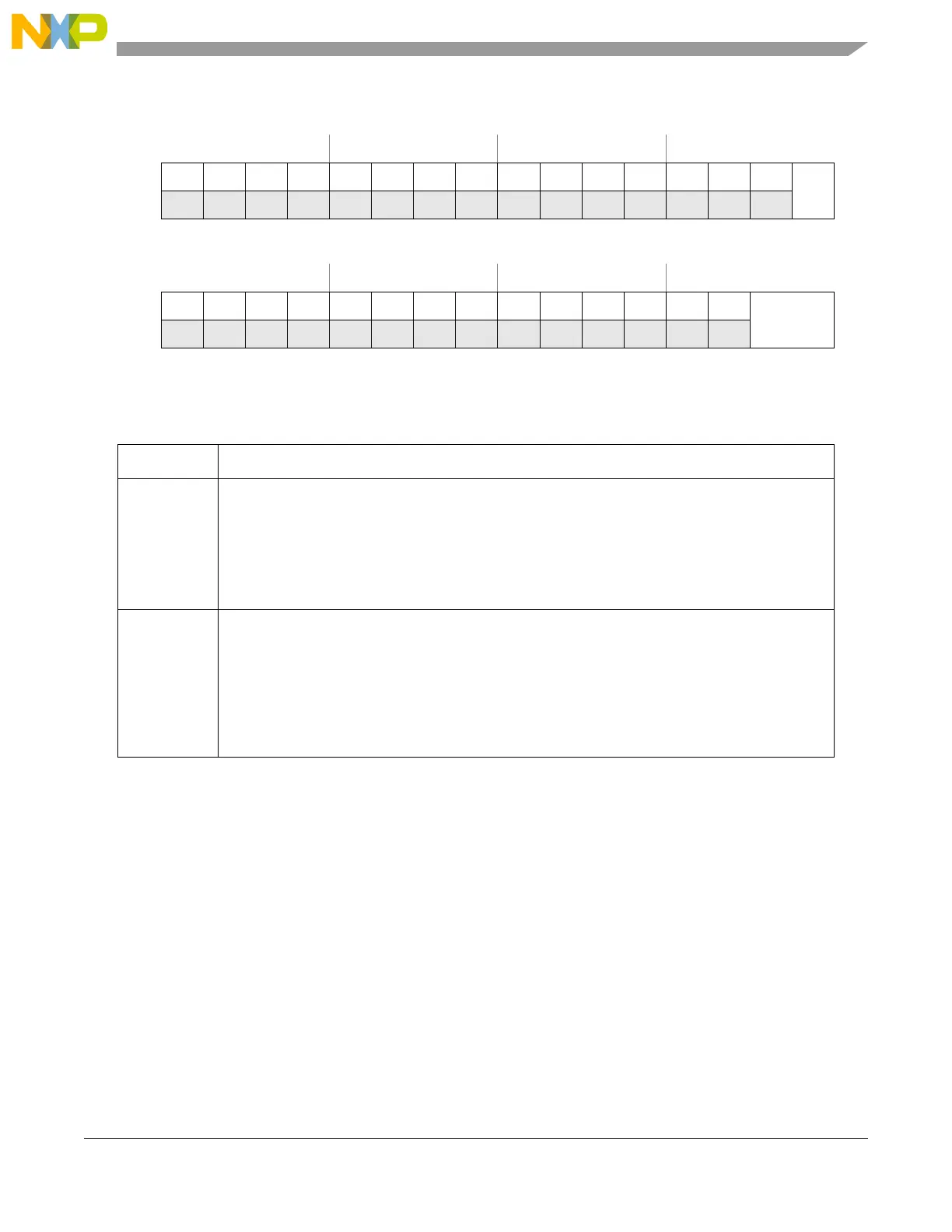

Offset 0x024 Access: Read/write

0123456789101112131415

R 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0

M0PFD

W

Reset Defined by NVPFAPR at CFlash Test Sector Address 0x203E00

16 17 18 19 20 21 22 23 24 25 26 27 28 29 30 31

R 0 0 0 0 0 0 0 0 0 0 0 0 0 0

M0AP

W

Reset Defined by NVPFAPR at CFlash Test Sector Address 0x203E00

Figure 27-41. PFlash Access Protection Register (PFAPR)

Table 27-60. PFAPR field descriptions

Field Description

M0PFD e200z0 core Master 0 Prefetch Disable

This field controls whether prefetching may be triggered based on the master number of the

requesting AHB master. This field is further qualified by the PFCR0[B0_Px_DPFE, B0_Px_IPFE,

Bx_Py_BFE] bits. For master numbering, see Table 17-1.

0: Prefetching may be triggered by this master

1: No prefetching may be triggered by this master

M0AP e200z0 core Master 0 Access Protection

These fields control whether read and write accesses to the flash memory are allowed based on the

master number of the initiating module. For master numbering, see Table 1 7-1.

00: No accesses may be performed by this master

01: Only read accesses may be performed by this master

10: Only write accesses may be performed by this master

11: Both read and write accesses may be performed by this master

Loading...

Loading...