MPC5604B/C Microcontroller Reference Manual, Rev. 8

Freescale Semiconductor 759

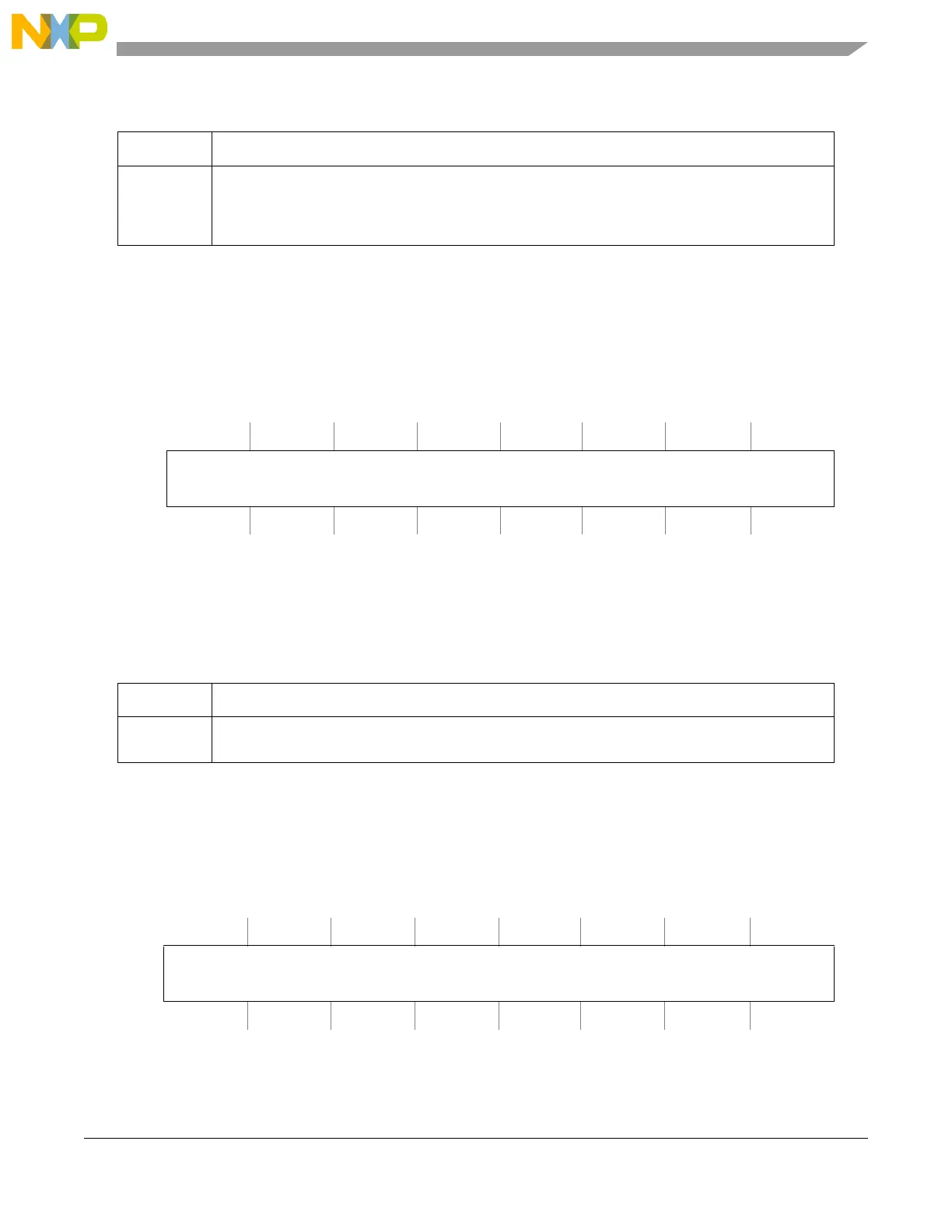

30.5.2.3 SWT Time-Out Register (SWT_TO)

The SWT Time-Out (SWT_TO) register contains the 32-bit time-out period. The reset value for this

register is device specific. This register is read only if either the SWT_CR.HLK or SWT_CR.SLK bits are

set.

Default counter value (SWT_TO_RST) is 1280 (0x00000500 hexadecimal) which correspond to around

10 ms with a 128 kHz clock.

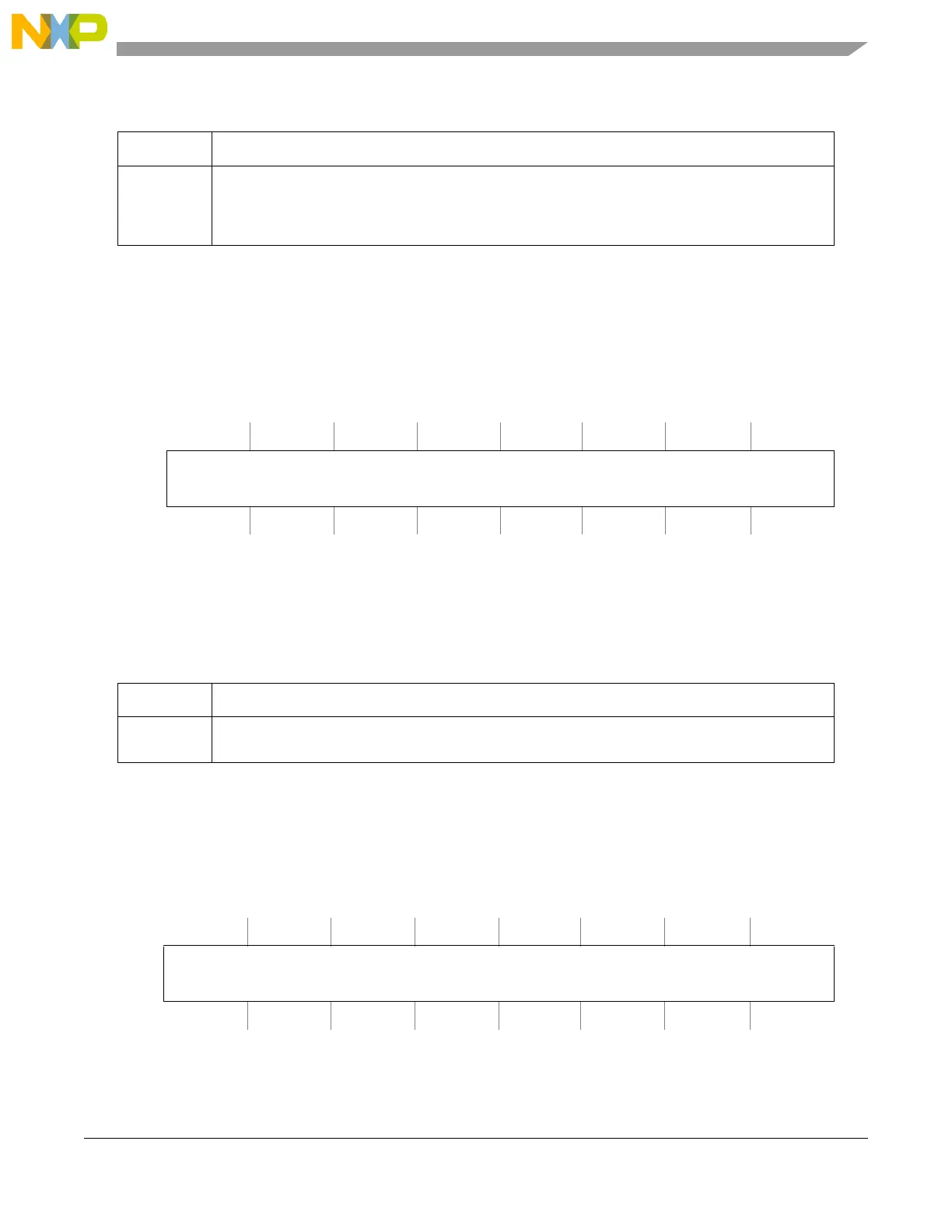

30.5.2.4 SWT Window Register (SWT_WN)

The SWT Window (SWT_WN) register contains the 32-bit window start value. This register is cleared on

reset. This register is read only if either the SWT_CR.HLK or SWT_CR.SLK bits are set.

Table 30-3. SWT_IR field descriptions

Field Description

TIF Time-out Interrupt Flag. The flag and interrupt are cleared by writing a 1 to this bit. Writing a 0 has

no effect.

0 = No interrupt request

1 = Interrupt request due to an initial time-out

Offset 0x008 Access: Read/Write

0 1 2 3 4 5 6 7 8 9 10111213141516171819202122232425262728293031

R

WTO

W

Reset

1

1

The reset value of the SWT_TO register is device specific.

00000000000000000000010100000000

Figure 30-3. SWT Time-Out Register (SWT_TO)

Table 30-4. SWT_TO Register field descriptions

Field Description

WTO Watchdog time-out period in clock cycles. An internal 32-bit down counter is loaded with this value or

0x100 which ever is greater when the service sequence is written or when the SWT is enabled.

Offset 0x00C Access: Read/Write

012345678910111213141516171819202122232425262728293031

R

WST

W

Reset

00000000000000000000000000000000

Figure 30-4. SWT Window Register (SWT_WN)

Loading...

Loading...