MPC5604B/C Microcontroller Reference Manual, Rev. 8

Freescale Semiconductor 811

NOTE

The EOC bits in DC1 must be programmed to trigger EVTO on watchpoint

occurrence for the EWC bits to have any effect.

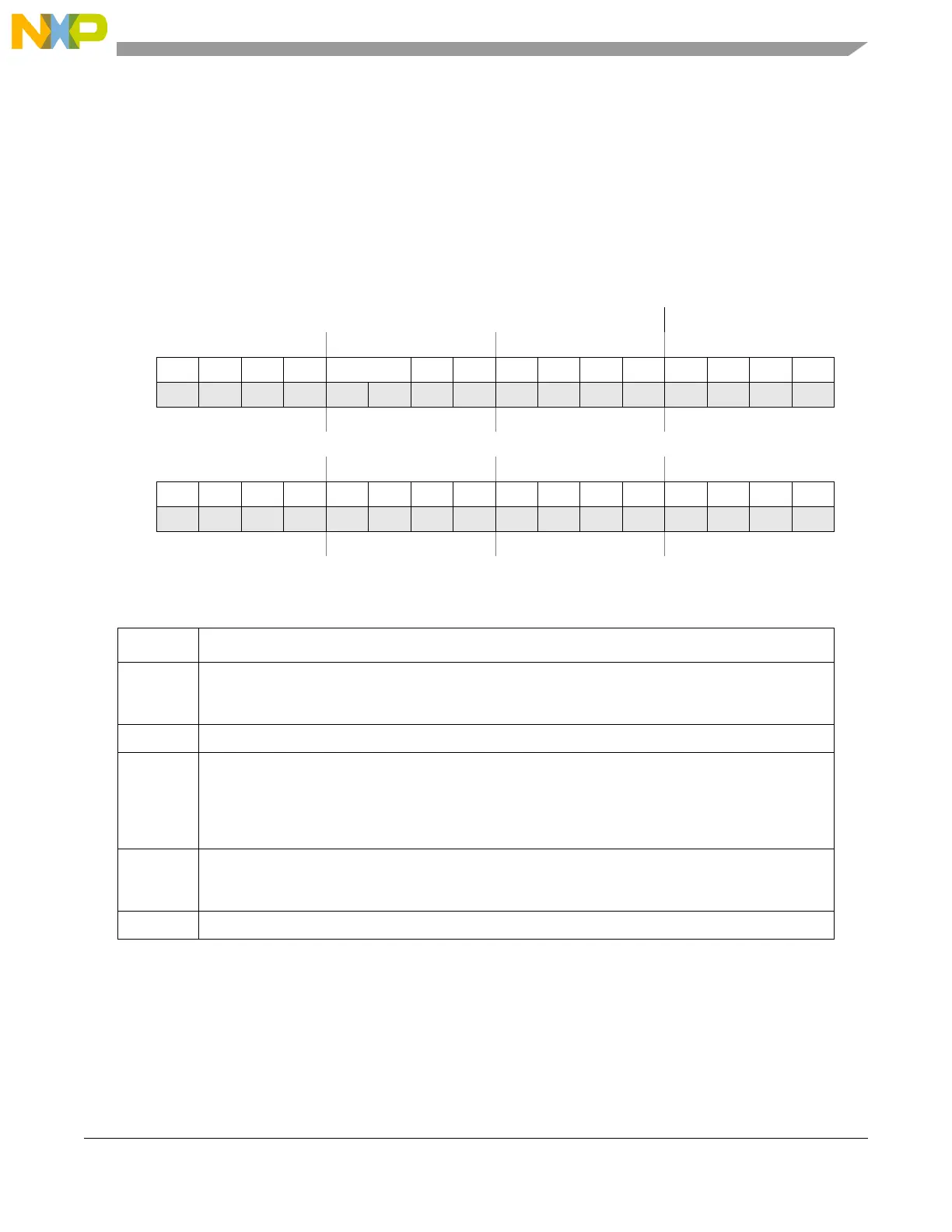

33.6.2.4 Development Status (DS) Register

The development status register is used to report system debug status. When debug mode is entered or

exited, or a core-defined low-power mode is entered, a debug status message is transmitted with

DS[31:24]. The external tool can read this register at any time.

Nexus Reg: 0x0004 Access: User read only

0123456789101112131415

R

DBG000 LPC CHK000000000

W

Reset0000000000000000

16 17 18 19 20 21 22 23 24 25 26 27 28 29 30 31

R0000000000000000

W

Reset0000000000000000

Figure 33-7. Development Status (DS) Register

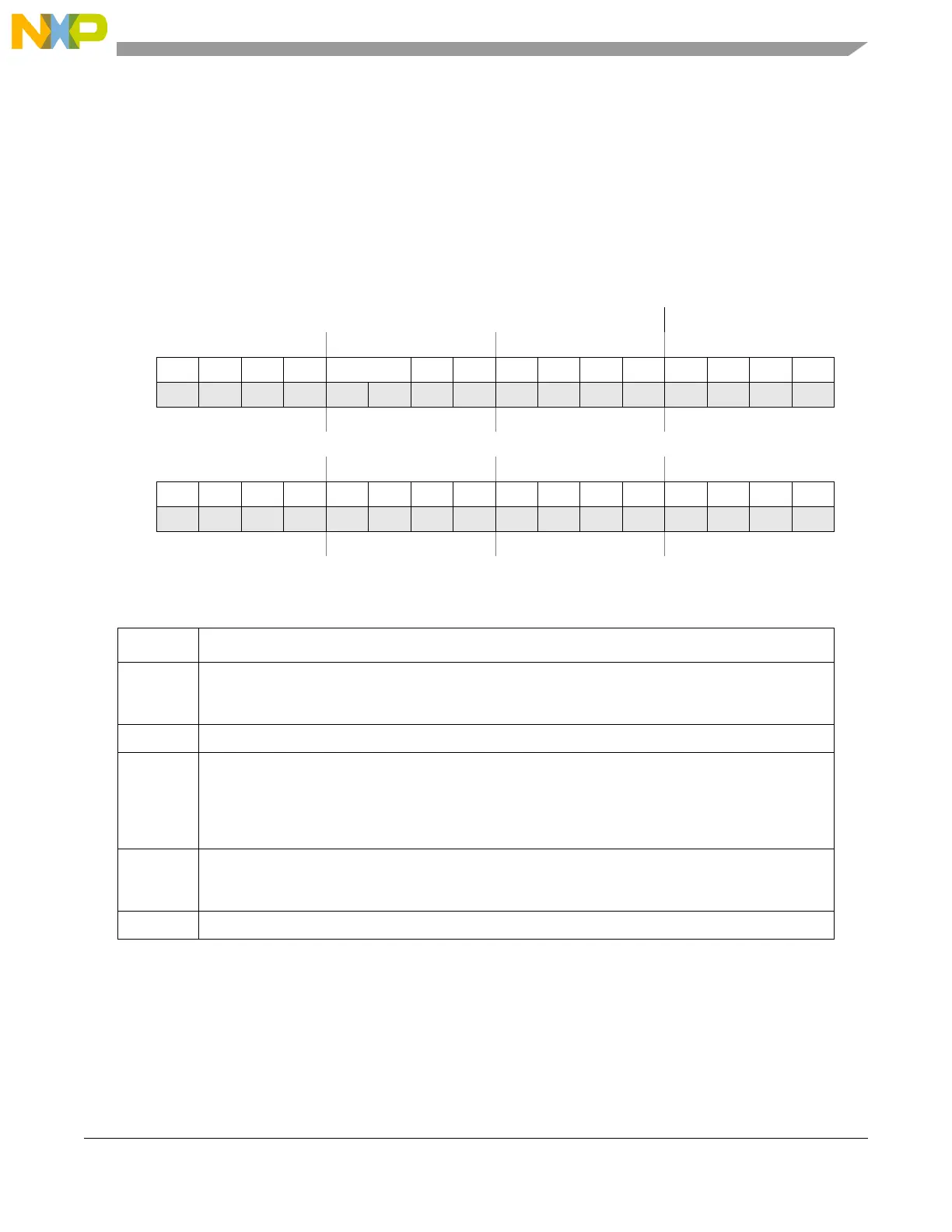

Table 33-7. DS field descriptions

Field Description

0

DBG

CPU Debug Mode Status

0 CPU not in debug mode

1 CPU in debug mode

1–3 Reserved

4–5

LPC[1:0]

CPU Low-Power Mode Status

00 Normal (run) mode

01 CPU in halted state

10 CPU in stopped state

11 Reserved

6

CHK

CPU Checkstop Status

0 CPU not in checkstop state

1 CPU in checkstop state

7–31 Reserved

Loading...

Loading...