MPC5604B/C Microcontroller Reference Manual, Rev. 8

812 Freescale Semiconductor

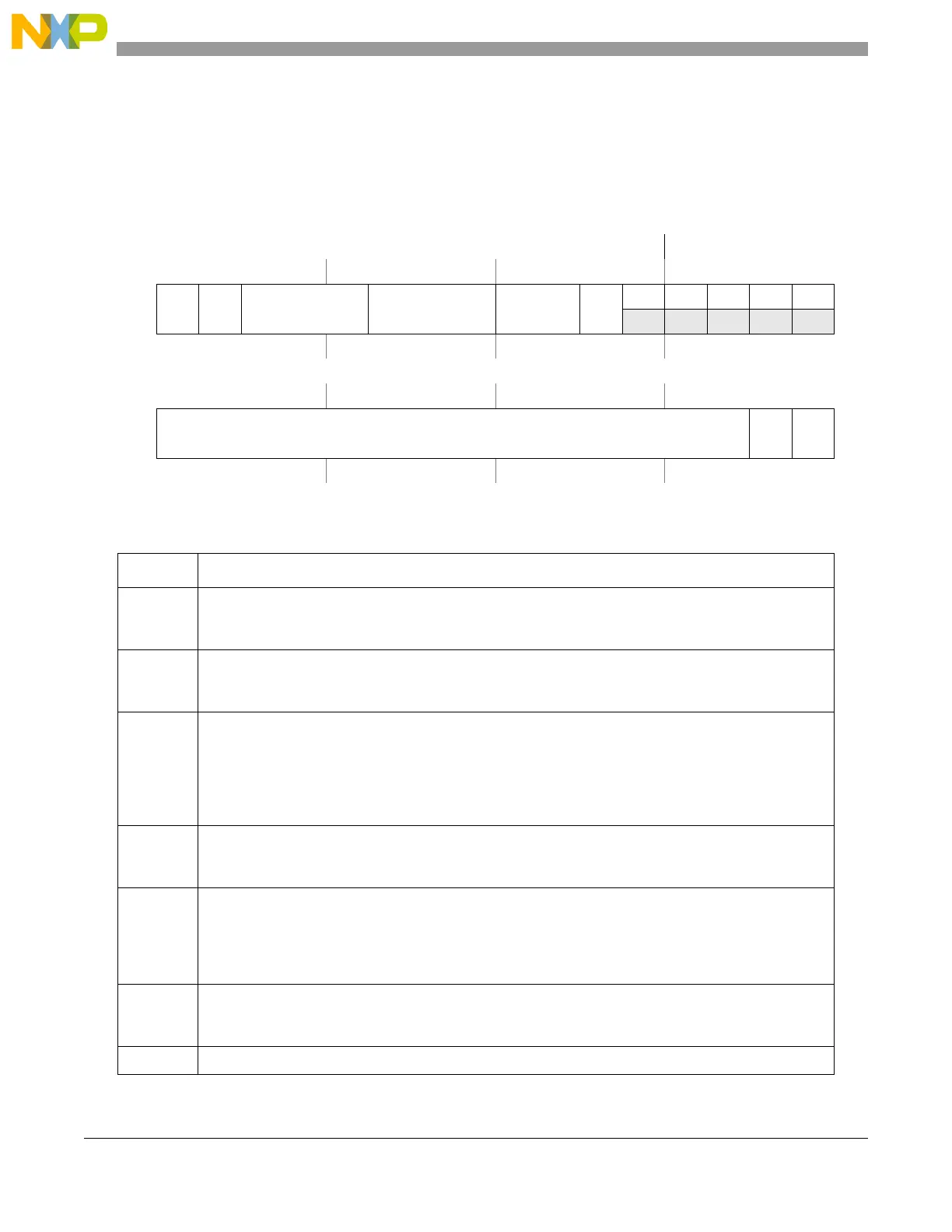

33.6.2.5 Read/Write Access Control/Status (RWCS) Register

The read write access control/status register provides control for read/write access. Read/write access

provides DMA-like access to memory-mapped resources on the system bus while the processor is halted

or during runtime. The RWCS register also provides read/write access status information as shown in

Table 33-9.

Nexus Reg: 0x0007 Access: User read/write

0123456789101112131415

R AC RW SZ MAP PR BST 0 0 0 0 0

W

Reset0000000000000000

16 17 18 19 20 21 22 23 24 25 26 27 28 29 30 31

R CNT ERR DV

W

Reset0000000000000000

Figure 33-8. Read/Write Access Control/Status (RWCS) Register

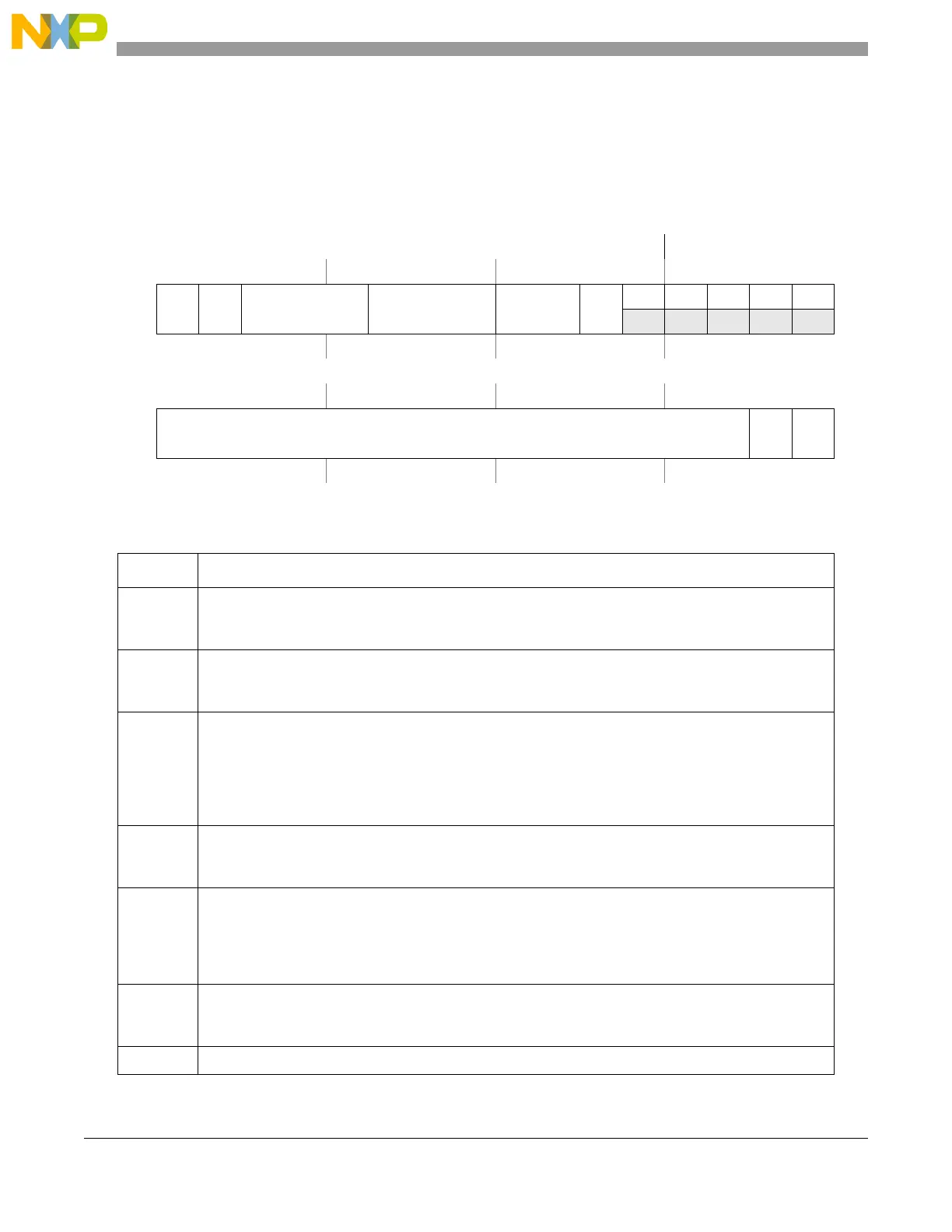

Table 33-8. RWCS field descriptions

Field Description

0

AC

Access Control

0 End access.

1 Start access.

1

RW

Read/Write Select

0 Read access

1 Write access

2–4

SZ[2:0]

Word Size

000 8-bit (byte)

001 16-bit (halfword)

010 32-bit (word)

011 64-bit (doubleword—only in burst mode)

100–111 Reserved (default to word)

5–7

MAP[2:0]

MAP Select

000 Primary memory map

001–111 Reserved

8–9

PR[1:0]

Read/Write Access Priority

00 Lowest access priority

01 Reserved (default to lowest priority)

10 Reserved (default to lowest priority)

11 Highest access priority

10

BST

Burst Control

0 Module accesses are single bus cycle at a time.

1 Module accesses are performed as burst operation.

11–15 Reserved

Loading...

Loading...