Optimizing for SIMD Integer Applications 4

4-9

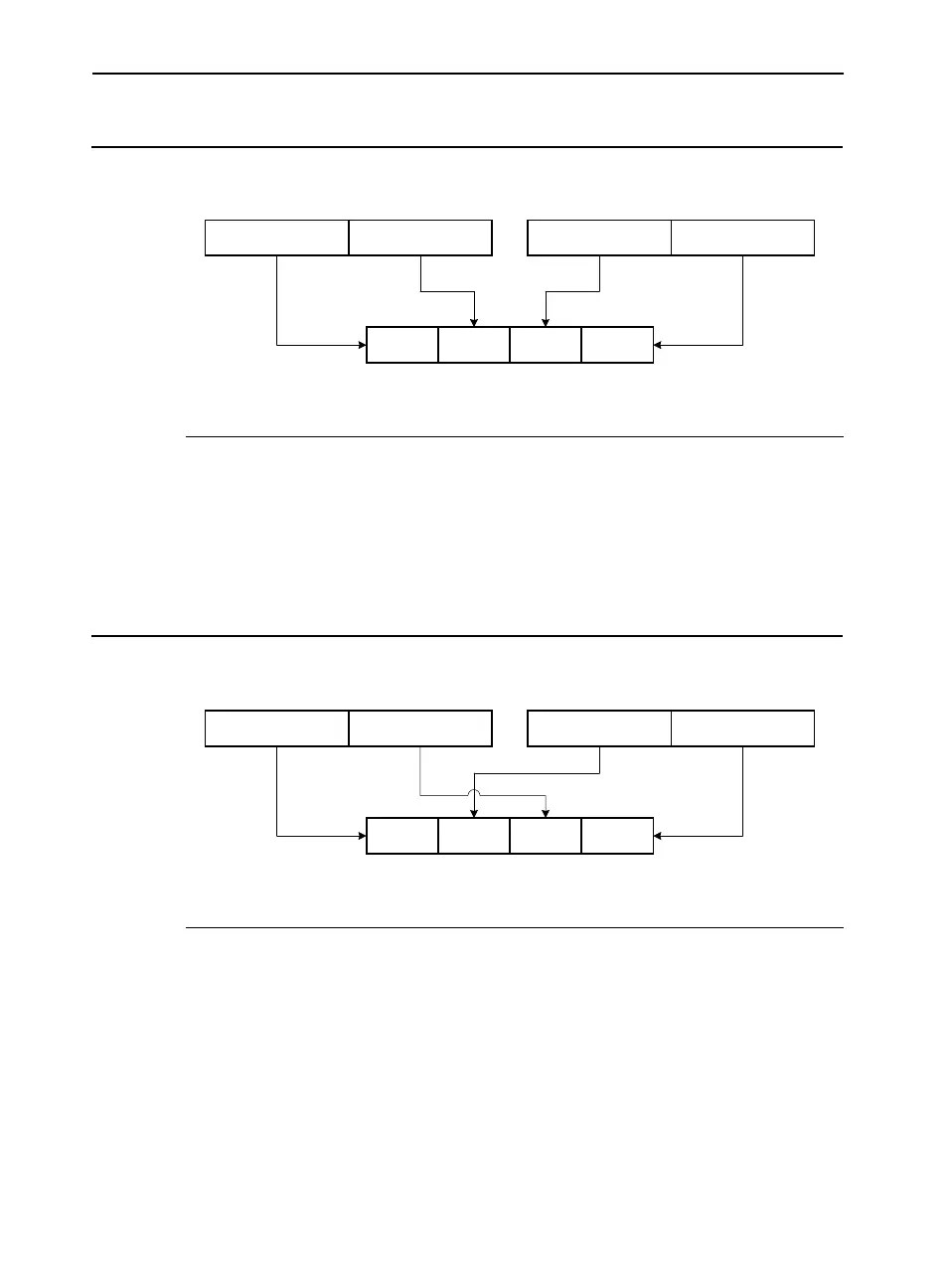

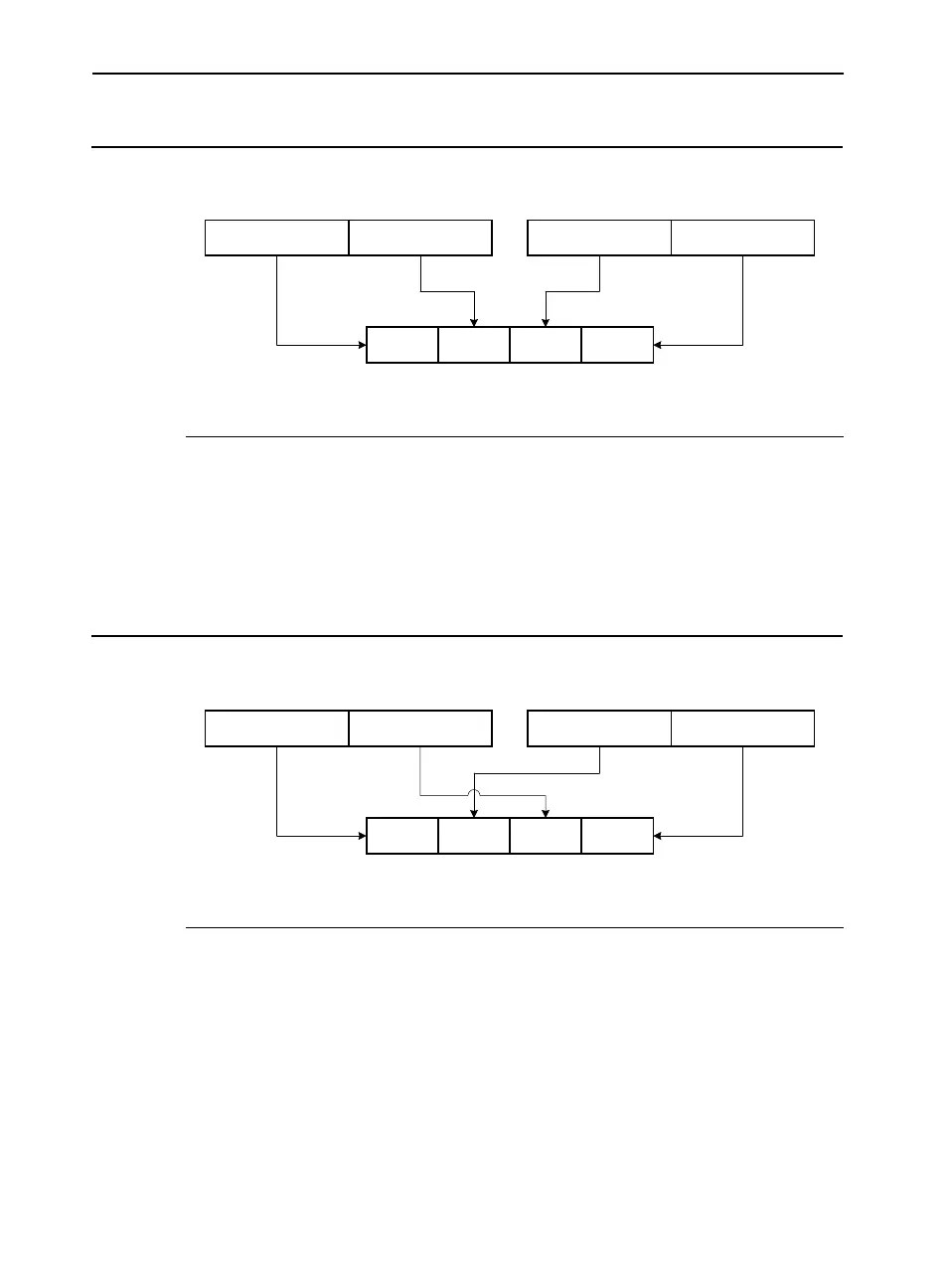

Figure 4-2 illustrates two values interleaved in the destination register,

and Example 4-4 shows code that uses the operation. The two signed

doublewords are used as source operands and the result is interleaved

signed words. The pack instructions can be performed with or without

saturation as needed.

Figure 4-1 PACKSSDW mm, mm/mm64 Instruction Example

Figure 4-2 Interleaved Pack with Saturation

OM15159

D C B A

D

1

C

1

B

1

A

1

mm/m64 mm

mm

OM15160

D C B A

D

1

B

1

C

1

A

1

MM/M64 mm

mm

Loading...

Loading...