IA-32 Intel® Architecture Optimization

B-18

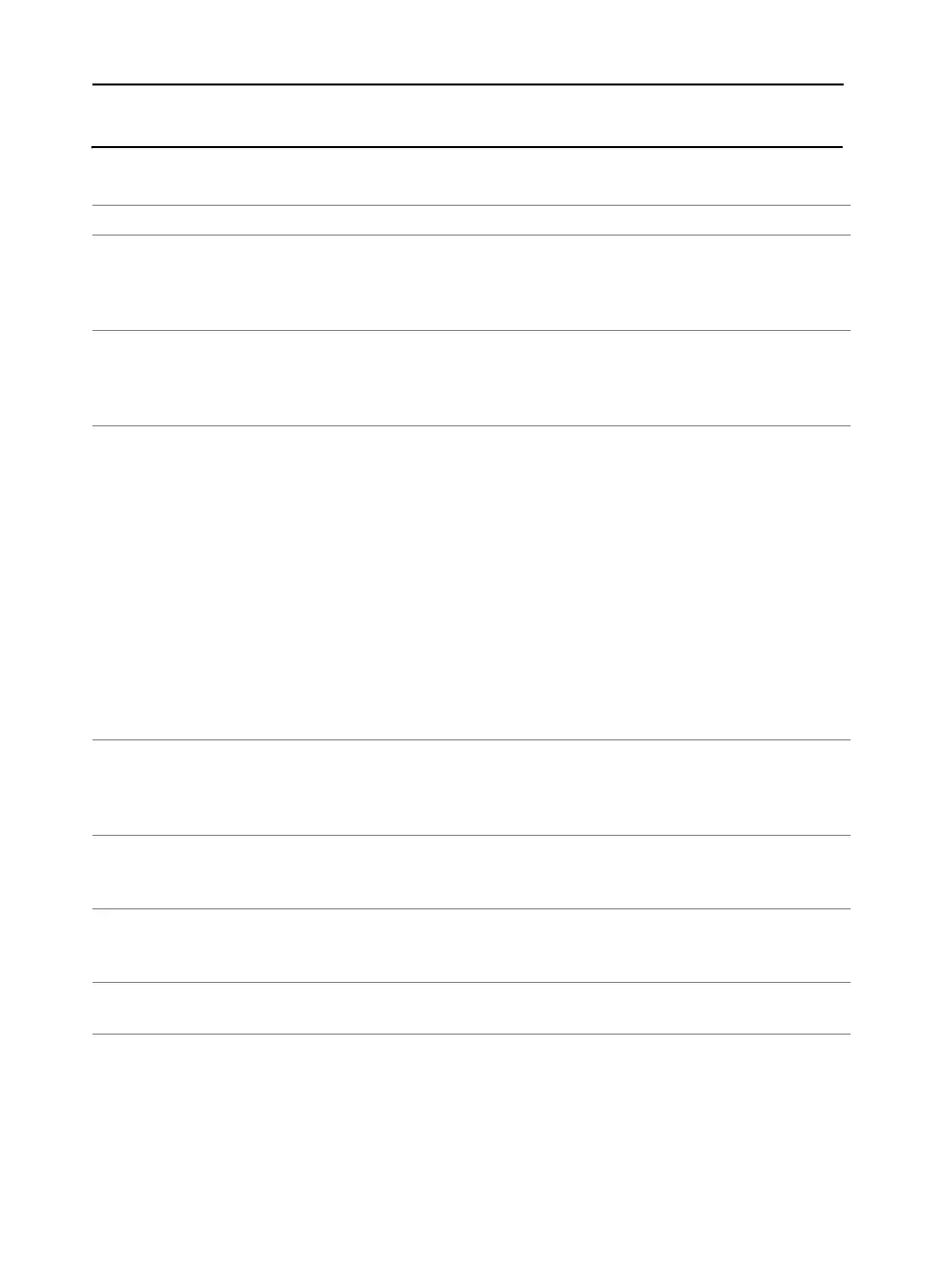

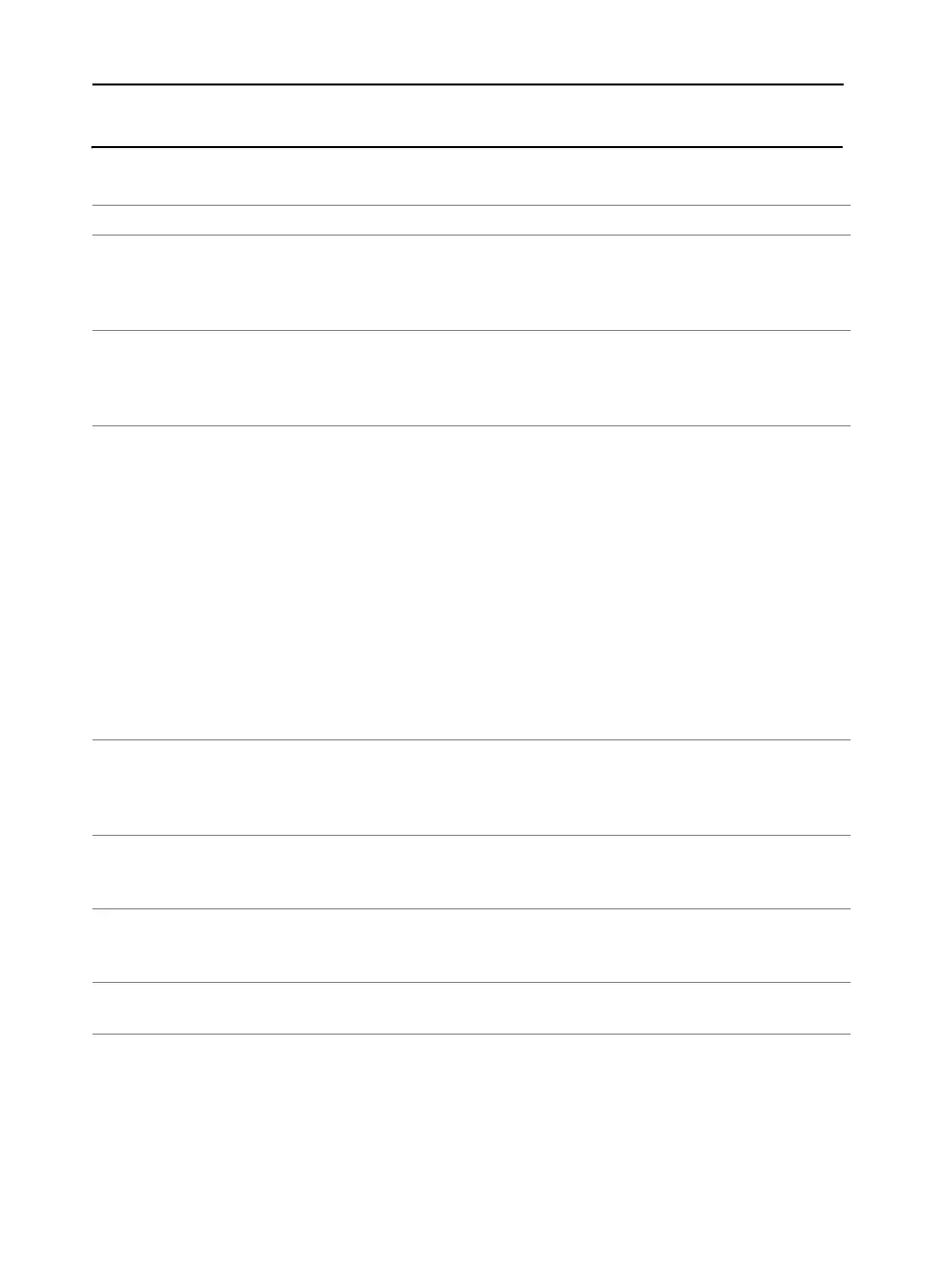

Table B-1 Pentium 4 Processor Performance Metrics

Metric Description

Event Name or Metric

Expression

Event Mask Value

Required

General Metrics

Non-Sleep

Clockticks

The number of

clockticks.while a

processor is not in

any sleep modes.

See explanation on how

to count clocks in section

“Counting Clocks”.

Non-Halted

Clockticks

The number of

clockticks that the

processor is in not

halted nor in sleep.

Global_power_events RUNNING

Instructions

Retired

Non-bogus IA-32

instructions executed

to completion. May

count more than

once for some

instructions with

complex uop flow

and were interrupted

before retirement.

The count may vary

depending on the

microarchitectural

states when counting

begins.

Instr_retired NBOGUSNTAG|

NBOGUSTAG

Non-Sleep CPI Cycles per

instruction for a

physical processor

package.

(Non-Sleep Clockticks) /

(Instructions Retired)

Non-Halted CPI Cycles per

instruction for a

logical processor.

(Non-Halted Clockticks) /

(Instructions Retired)

μops Retired Non-bogus μops

executed to

completion

uops_retired NBOGUS

UPC μop per cycle for a

logical processor

μops Retired/ Non-Halted

Clockticks

continued

Loading...

Loading...