IA-32 Intel® Architecture Optimization

9-18

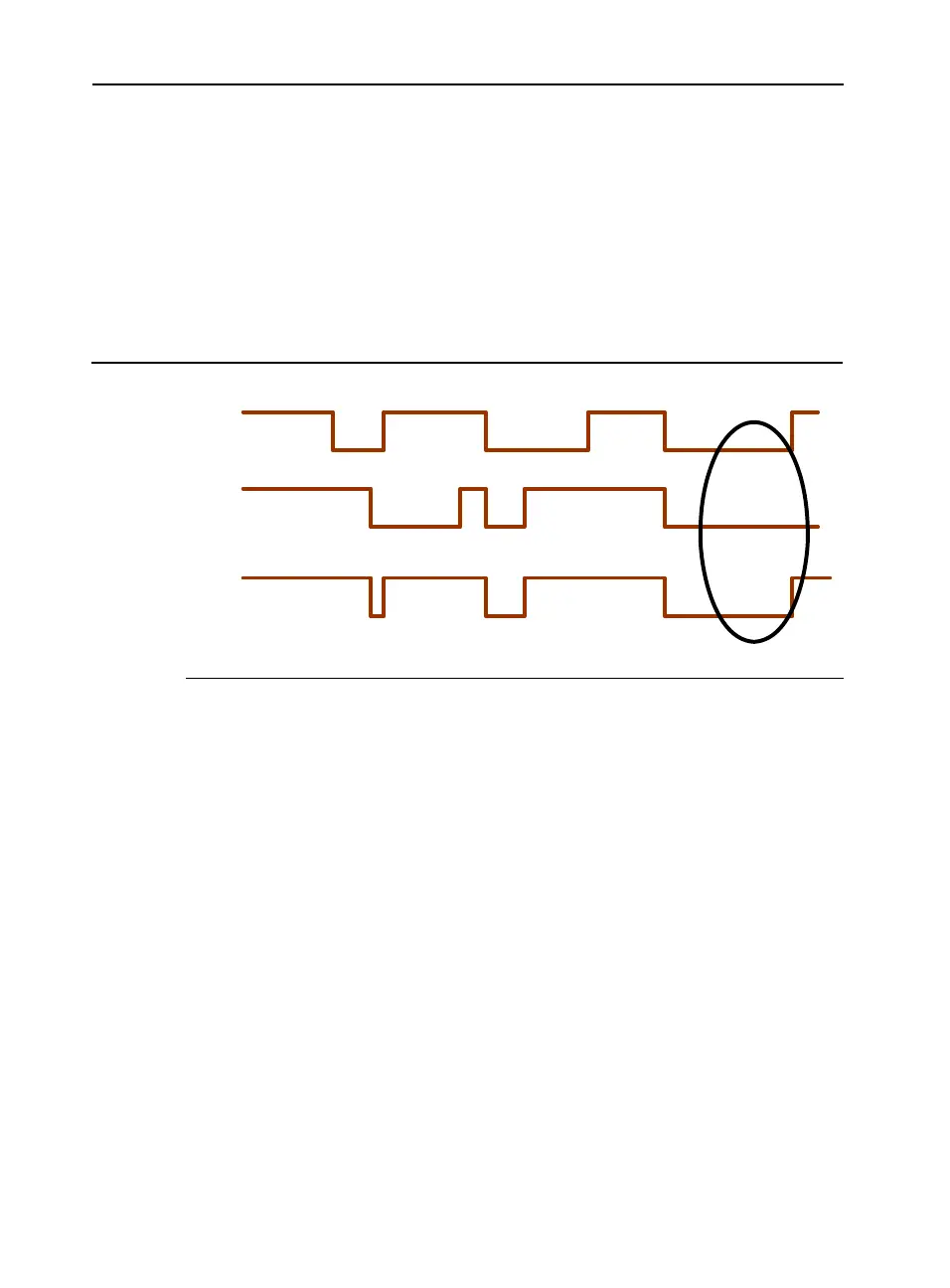

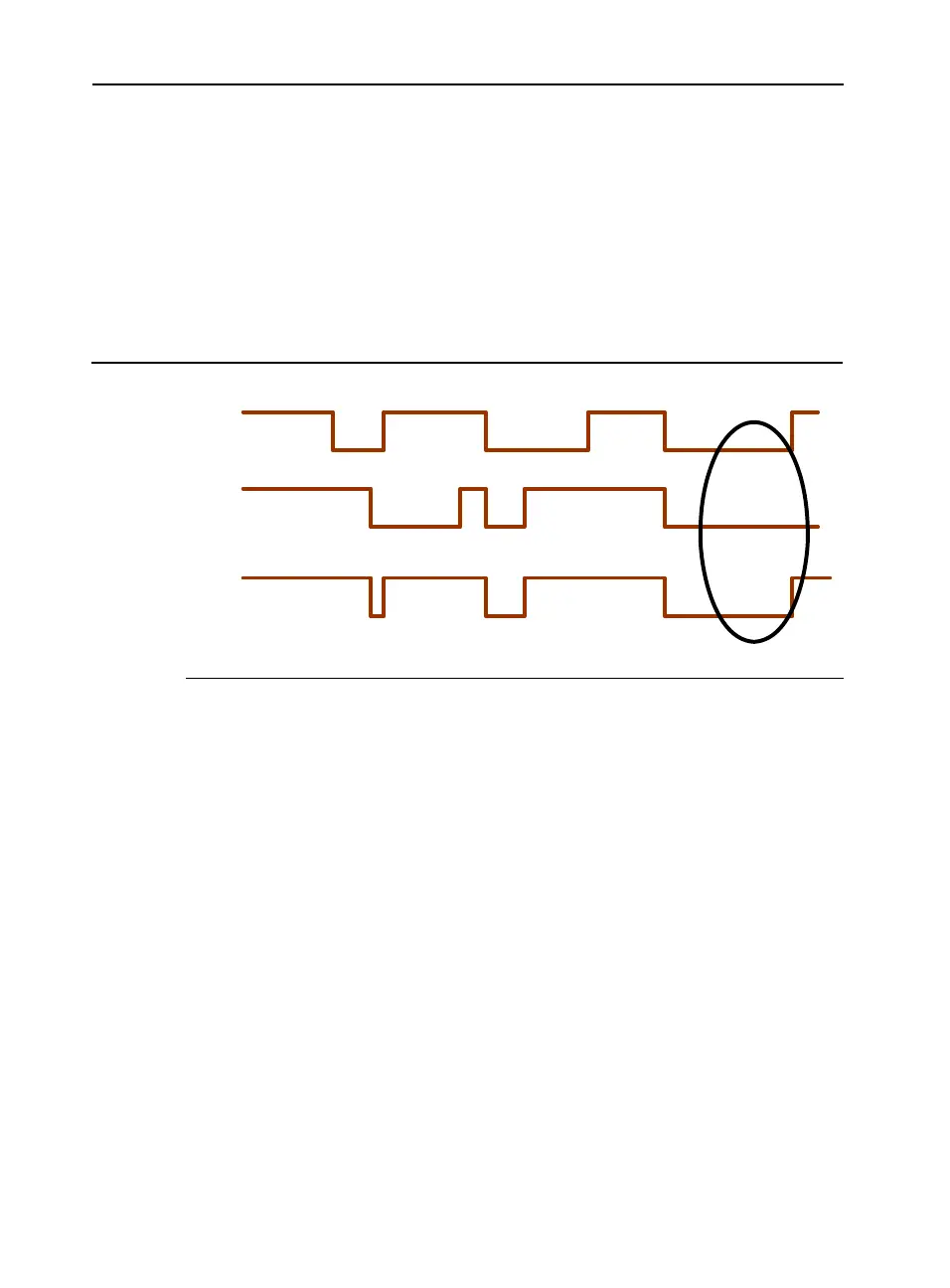

processor to enter the lowest possible C-state type

(lower-numbered C state has less power saving). For example,

if Core 1 meets the requirement to be in ACPI C1 and Core 2

meets requirement for ACPI C3, multi-core-unaware OS

coordination takes the physical processor to ACPI C1. See

Figure 9-6.

2. Enabling both core to take advantage of Intel Enhanced Deeper

Sleep:

To best utilize processor-specific C-state (e.g., Intel Enhanced

Deeper Sleep) to conserve battery life in multithreaded

applications, a multi-threaded applications should synchronize

threads to work simultaneously and sleep simultaneously using

OS synchronization primitives. By keeping the package in a

fully idle state longer (satisfying ACPI C3 requirement), the

physical processor can transparently take advantage of

processor-specific Deep C4 state if it is available.

Multi-threaded applications need to identify and correct

load-imbalances of its threaded execution before implementing

coordinated thread synchronization. Identifying thread

Figure 9-6 Progression to Deeper Sleep

Thread 1

(core 1)

Thread 2

(core 2)

CPU

Active

Sleep

Active

Active

Sleep

Sleep

Deeper

Sleep

Loading...

Loading...